# An Efficient Timestamp-Based Monitoring Approach to Test Timing Constraints of Cyber-Physical Systems

Mohammadreza Mehrabian Arizona State University Mohammadreza.Mehrabian@asu.edu

> Aviral Shrivastava Arizona State University Aviral.Shrivastava@asu.edu

Edward Griffor National Institute of Standards and Technology edward.griffor@nist.gov

> John C. Eidson University of California Berkeley eidson@eecs.berkeley.edu

Mohammad Khayatian Arizona State University mkhayati@asu.edu

Ya-Shian Li-Baboud National Institute of Standards and Technology ya-shian.li-baboud@nist.gov

> Hugo A. Andrade Xilinx hugoa@xilinx.com

> > Anand Dhananjay National Institute of Standards and Technology dhananjay.anand@nist.gov

## ABSTRACT

Formal specifications on temporal behavior of Cyber-Physical Systems (CPS) is essential for verification of performance and safety. Existing solutions for verifying the satisfaction of temporal constraints on a CPS are compute and resource intensive since they require buffering signals from the CPS prior to constraint checking. We present an online approach, based on Timestamp Temporal Logic (TTL), for monitoring the timing constraints in CPS. The approach reduces the computation and memory requirements by processing the timestamps of pertinent events reducing the need to capture the full data set from the signal sampling. The signal buffer size bears a geometric relationship to the dimension of the signal vector, the time interval being considered, and the sampling resolution. Since monitoring logic is typically implemented on Field Programmable Gate Arrays (FPGAs) for efficient monitoring of multiple signals simultaneously, the space required to store the buffered data becomes the limiting resource. The monitoring logic, for the timing constraints on the Flying Paster (a printing application requiring synchronization between two motors), is illustrated in this paper to demonstrate a geometric reduction in memory and computational resources in the realization of an online monitor.

## **CCS CONCEPTS**

• Computer systems organization → Embedded and cyberphysical systems; Embedded software;

## **1** INTRODUCTION

Cyber-Physical Systems (CPS) are becoming an integral part of human life. While it is desirable to build systems with guarantees of correct behavior, it is becoming increasingly difficult, due to the increasing scale, complexity, and non-deterministic nature of applications, networks, processing platforms, and unpredictable interactions with the physical world [1]. One promising approach to ensure that the system is executing in a safe manner is to monitor the system at runtime [2]. In online monitoring, application constraints are continuously monitored during runtime. Online monitoring can be used to analyze the system behavior in the field and check for bugs in the design. In contrast, offline monitoring in real systems utilizes forensic analysis and therefore does not offer the ability for timely correction of system deviations. Although offline monitoring can be useful, online monitoring is desirable since it may be possible to detect early violations and prevent a system from reaching an unsafe state [3].

Ahmed Mousa

Arizona State University

aomoussa@asu.edu

Patricia Derler

National Instruments

patricia.derler@ni.com

Marc Wiess

Marc Weiss Consulting

marcweissconsulting@gmail.com

Since the correct operation of many CPS applications relies upon the correct timing of the system, both functional and temporal requirements of a CPS must be monitored [4]. This paper focuses on the monitoring of timing constraints in CPS. Many existing monitoring systems define system timing constraints using Signal Temporal Logic (STL) [5]. STL allows users to define timing constraints on real-valued signals relative to current time. For example, in the Globally constraint in STL, a user could specify a timing constraint  $\phi := \Box_{[2,6]}(|x[t]| < 2)$ , which means that a property  $\phi$  will be true at time  $t = \tau$ , iff the real-valued signal  $x[t] \in [-2, 2] \ \forall \tau \in [2, 6]$ . To compute whether the timing constraint  $\phi$  was met at time  $t = \tau$ , the conventional approaches [5-10] record the value of the signal x[t] at all times in the interval  $t \in [\tau + 2, \tau + 6]$ . The signal values are compared against the constraint, (|x[t]| < 2), to determine if the requirements are satisfied within the time interval  $[\tau + 2, \tau + 6]$ . The constraint evaluation is repeated for each sampling period.

Often, existing monitoring systems are implemented in a simulation. To test real-time systems, FPGA (Field Programmable Gate Array) implementation has the potential to minimize computational latencies and allows for simultaneous monitoring of multiple signals, while supporting the flexibility for modifications and upgrades. The scheme by Jakšić *et al.* [11] was implemented on FPGAs. However, for FPGAs, the available memory to store the signal histories and perform the computation becomes the main bottleneck.

To evaluate how practical the existing state-of-the-art monitoring schemes are, we built a model of a Flying Paster application. We specified seven timing constraints to minimize the amount of

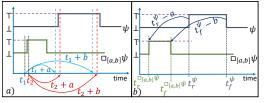

Figure 1: *Globally*: a) Conventional monitoring calculation at each time-step, b) TMA uses two subtractions per pulse.

unused paper while ensuring sufficient time to paste and splice the paper of the new roll before the first roll expires. The implemented test code to evaluate against the timing constraints using the (latest) *Counters* approach by Jakšić *et al.* [11], could not be compiled due to insufficient memory on the commercial off-the-shelf (COTS) FPGA board with 82, 000 flip-flops (FFs) and 41, 000 look-up tables (LUTs), at a sampling rate of 20 kHz. In CPS, examples of systems using high sampling rates include power systems where IEC 61869-9 specifies sampling rates at 4.8 kHz for Alternating Current (AC) and up to 96 kHz for Direct Current (DC) measurements [12].

In this paper, we propose a more efficient online approach for monitoring the timing constraints of CPS, Timestamp-based Monitoring Approach. The key improvement is rather than evaluating a constraint at each sampling period, TMA only computes the constraint satisfaction at the occurrence of relevant events extracted from monitored signals. For constraint  $\phi := \Box_{[2,6]}(|x[t]| < 2)$ , TMA identifies x[t] as the signal-of-interest when x[t] goes above or below 2 V. Accordingly,  $\phi$  is re-computed only at the occurrence of the next event-of-interest. TMA can monitor all seven timing constraints of Flying Paster model application at a sampling rate of 20 kHz, using only 11% of the FFs and 11.5% of LUTs on the same FPGA.

In general, for a constraint that is defined over a time interval of T , and must be monitored for the duration of experiment d, with a sampling frequency of f, the conventional approach requires O(Tfd) computation time. The requirements of both, computation time and memory, depending on the interval size and the sampling rate. In contrast, our approach has a complexity of O(k), where k is the maximum number of events during time *d*. Case in point, both the computation and memory requirement of the monitoring logic for implementing a Globally constraint using the Jakšić et al. approach [11] increases with the interval size of the Globally operator, while the monitoring logic of TMA is independent of the time interval, and scales well. Another important point to note is that although event-based constraints (e.g, whenever signal s1 rises above 2.5 V, the signal s<sub>2</sub> should fall below 1 V in less than 2 s.) can be specified in STL the logic that is generated can be complex and resource intensive since an event-based constraint is composed of several STL temporal operators. On the other hand, event-based temporal constraints are specified using TTL, Simultaneity, Chronological, Phase, Frequency, Latency, among others [13]. TTL provides for a more intuitive and simple specification (e.g.,  $\mathcal{L}(\langle s_1, 2.5, \nearrow \rangle, \langle s_2, 1, \nearrow \rangle) < 2)$ . In this paper, we apply two of the primitives, namely Latency and Simultaneity, to illustrate the online monitoring approach.

## 2 RELATED WORK

Conventional monitoring methods have high memory usage and processing time requirements since they evaluate timing constraints

at every time-step. Offline tools for analyzing the timing requirements in CPS have been implemented in Breach[14], and S-Taliro [15]. Both tools record simulation data and evaluate timing constraints after the simulation has finished. Figure 1.a depicts the conventional monitoring approach. It plots the value of Boolean signal  $\psi$  along the time axis at the top. To evaluate the constraint  $\Box_{[a,b]}\psi$  at time  $t_1$ , the existing techniques look at the entire interval  $[t_1 + a, t_1 + b]$ . If the signal is *true* for the entire duration, the constraint is met at  $t_1$ . Since the signal  $\psi$  was *false* for some time (just after  $t_1 + a$ ), the constraint  $\Box_{[a,b]}\psi$  is not met at time  $t_1$ . However, the constraint is met at  $t_2$ . The computation required to evaluate this constraint is  $O(Tf^2)$ , where T is the time interval over which the temporal operator is defined, which in this case, is T = b - a, and f is the sampling frequency. The memory buffer required for this computation will be O(Tf). If there is a constraint with P temporal operators, and w signals, then the amount of computations is  $O(TPwf^2)$ , while the amount of buffer needed will be O(TPwf). To monitor one timing constraint with four temporal operators defined over an interval of 100 s, with a system sampling rate and analog to digital converter (ADC) resolution of 20 kHz ( $t_s = 50 \ \mu s$ ) and 12-bit, we need 12 MB of memory ( $M = 4 \times \frac{100}{50 \ \mu s} \times \frac{12}{8}$ ). Primarily, because of the computational complexity, evaluating temporal constraints in real-time is not scalable. Practical CPS applications, such as power generation and distribution have numerous constraints, each containing multiple, high-frequency data signals to be monitored simultaneously, and may have evaluation time intervals over extended durations.

Recognizing the high overhead, AMT [16] proposed an incremental approach to compute the constraints at a segment granularity. However, they can reduce the complexity only by the factor of the granularity. An incremental method was proposed by Deshmukh *et al.* [10] where timing constraints are evaluated by traversing the parse tree generated for STL formulas. They optimize their calculation by eliminating repetitive computations.

While all the previous approaches were implemented in simulation, Jakšić et al. [11] implemented a monitoring method called Counters algorithm on FPGA. The Counters algorithm reduces the computation complexity from  $O(n^2)$  to  $O(n \log(n))$ , where *n* is the size of time interval of the temporal constraints. Although Jakšić et al. showed a way to reduce memory usage, the storage remains a concern (even for bounded constraints). This technique converts future STL operators into past ones and translates all constraints such that their interval starts from zero. Then, a counter is dedicated for measuring the duration of a positive pulse in each interval. The number of needed counters depends on the variability of the monitored signal and the length of the interval bound (a). In each time-step, the active counter is incremented to measure the duration of positive pulses. The maximum number of counters is  $\lceil \frac{2a}{b-a+1} \rceil$ where each counter has  $\lceil \log_2 a \rceil$  bits. For example,  $\Box_{\lceil 5000, 5001 \rceil} \psi$ needs 5000 counters, each with  $\log_2 5000 = 13$  bits. Therefore, we need around 8 kB to monitor just one signal. In contrast, to monitor the same constraint using TMA, only the last two timestamps of the events-of-interest and the last two timestamps of the result are needed. Therefore, four 32 - bit variables for each operator is needed, which is independent of interval length and sampling rate, and a small memory footprint for the state machine. We need one

An Efficient Timestamp-Based Monitoring Approach to Test Timing Constraints of Cyber-Physical Systems

DAC'18, July 2018, San Francisco, California, USA

state machine per operator and the size of each state machine is very small since it needs only 2 bits to store the state.

STL expressions are often combined and/or nested and must be evaluated recursively. Additionally, although STL has the capability to express event-based timing constraints, they are constructed out of a variety of level-based timing constraints. In order to represent only one event (rising or falling) in STL, we should use past and future operators together in one expression<sup>1</sup>. In contrast, TTL can easily express the event timing constraint so that the implementation test code can be succinct as well.

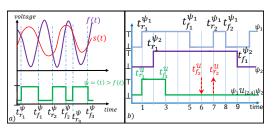

## **3 TIMESTAMP MONITORING APPROACH**

We use TTL to specify the application timing constraints, since TTL succinctly expresses both event-based and level-based timing constraints commonly used in CPS. TTL considers temporal behavior of analog signals upon a given threshold function in level-based timing constraints. Also, this logic can express event-based timing constraints where the time at which a signal value changes (e.g.  $\mathcal{L}(\langle s_1, 2.5, \nearrow \rangle, \langle s_2, 1, \nearrow \rangle) > 2$ , whenever a rising  $s_1$  signal *crosses* 2.5 V, a rising s<sub>2</sub> shall not cross 1 V earlier than 2 s). Hence, we first convert analog signals to discrete event boolean signals by the method in [13, 17]. Therefore, we have  $\mathbb{R} \to \mathbb{B}$  to transform the analog to boolean signals. Then, timestamps corresponding to rising and falling edges are extracted. We define finite sets of rising edges  $\Gamma_r$  and falling edges  $\Gamma_f$  for a boolean signal,  $\psi$ , as:  $\Gamma_r = \{t_{r_1}^{\psi}, ..., t_{r_n}^{\psi}\}$ and  $\Gamma_f = \{t_{f_1}^{\psi}, ..., t_{f_n}^{\psi}\}$  where  $t_{r_i}^{\psi}$  and  $t_{f_i}^{\psi}$  are the timestamps for the  $i^{th}$  rising and falling edge on  $\psi.$  Figure 2.a depicts a boolean signal  $\psi$ , which is created when the analog signal s(t) crosses a threshold, f(t) that shows after threshold crossing, the boolean signal is described by  $t_{r_i}^{\psi}$  and  $t_{f_i}^{\psi}$ , (i = 1, ..., n). Now, we present a boolean signal as a tuple consisting of an initial state ( $\psi_{init}$ ), a set of rising edges ( $\Gamma_r$ ) and a set of falling edges ( $\Gamma_f$ ):  $\psi = (\psi_{init}, \Gamma_r, \Gamma_f)$

Figure 2: a) Crossing signal s(t) with function f(t), b) Illustration for *Until* computation by TMA.

The *differentiate* operator  $(\bowtie)$ ,  $\varphi = \bowtie (\psi)$  extracts the rising edge of a boolean signal  $\psi \in \mathbb{B}$  where the value of  $\varphi$  is 1 if  $(\psi(t^+) \oplus \psi(t)) \land \neg \psi(t) = \top$ , and  $\bot$  otherwise.  $\oplus$  is the XOR operator and,  $t^+$  refers to the right neighborhood (the next time-step) of signal at time *t*. By applying differentiate operator on a boolean signal  $\psi$  ( $\varphi = \bowtie \psi$ ), we provide another boolean signal,  $\varphi$ , which is *true* for a short period (sampling time) and *false* otherwise. Since this operator provides the event set,  $\Theta^{\varphi}$ , it contains just the timestamps which show the time of *events* (not rising and falling) as:  $\Theta^{\varphi} = \{\theta_1^{\varphi}, ..., \theta_n^{\varphi}\}$ .

## 3.1 Level-based Approach

In this section, we introduce three algorithms executed at each rising and falling edge to define the set of timestamps for online constraint evaluation of level-based TTL operators.

3.1.1 Globally Rules. Given a boolean signal  $(\psi)$  expressed with a set of rising and falling edges  $\Gamma_r^{\psi}$  and  $\Gamma_f^{\psi}$  respectively, for every new pair of timestamps, generated from the signal threshold crossings, we update the set of rising and falling edges for  $\Box_{[a,b]}\psi$  ( $\Gamma_r^{\Box}$ and  $\Gamma_f^{\Box}$ ) by applying Algorithm 1 on the received timestamps. The new  $\Box_{[a,b]}\psi$  rising and falling edges are computed based on the most recent  $t_r^{\psi}$  (expressed as the current rising edge timestamp on  $\psi$ ),  $t_f^{\psi}$  (expressed as the current falling edge timestamp on  $\psi$ ) as well as the values of *a* and *b*. The computed rising and falling edges are only added to  $\Gamma_r^{\Box}$  and  $\Gamma_f^{\Box}$  if its timestamp for the rising edge is less than that of the falling edge.

| <b>Algorithm 1</b> Globally $(t_r^{\psi}, t_f^{\psi}, \mathbf{a}, \mathbf{b})$ |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1: $t_{r_i}^{\Box} = t_r^{\psi} - a$                                           |  |  |  |  |  |  |

| 2: $t_{f_i}^{\Box} = t_f^{\psi} - b$                                           |  |  |  |  |  |  |

| 3: if $t_{r_i}^{\Box} < 0$ then                                                |  |  |  |  |  |  |

| 4: $t_{r_i}^{\Box} = 0$                                                        |  |  |  |  |  |  |

| 5: end if                                                                      |  |  |  |  |  |  |

| 6: if $t_{r_i}^{\Box} \leq t_{f_i}^{\Box}$ then                                |  |  |  |  |  |  |

| 7: $\Gamma_r^{\Box} = \Gamma_r^{\Box} + \{t_{r_i}^{\Box}\}$                    |  |  |  |  |  |  |

| 8: $\Gamma_f^{\square} = \Gamma_f^{\square} + \{t_{f_i}^{\square}\}$           |  |  |  |  |  |  |

| 9: end if                                                                      |  |  |  |  |  |  |

3.1.2 Eventually Rules. A boolean signal ( $\psi$ ) expressed with,  $\Gamma_r^{\psi}$  and  $\Gamma_f^{\psi}$ , for every new pair of timestamps, we update the set of rising and falling edges by applying Algorithm 2. The calculated timestamps are only added to the set under the constraint; a rising edge must occur after the last falling edge. Also, if the last computed falling is in the range of new pulse, the last falling should be replaced with the new falling edge to append the last pulse on the result.

3.1.3 Until Rules. Given two boolean signals,  $\psi_1$  and  $\psi_2$ , with new rising and falling edges  $t_r^{\psi_1}, t_r^{\psi_2}, t_f^{\psi_1}$  and  $t_f^{\psi_2}$ , we update the set of rising and falling edges for  $\psi_1 \mathcal{U}_{[a,b]} \psi_2$  ( $\Gamma_r^{\mathcal{U}}$  and  $\Gamma_f^{\mathcal{U}}$ ) using Algorithm 3 with the incoming pairs of timestamps. The new rising and falling edges for Until are computed in the first 2 lines. Starting at line 3, new edges are either appended or discarded, depending on whether or not they comply with the signals. For example, any negative time value and any set of edges with a falling happening before a corresponding rising edge indicate the constraint is not satisfied. Similarly, any edge with rising that comes before the falling edge of the previous set is discarded and the previous falling is replaced with the new falling since the last positive pulse should be extended to the new falling edge. A pair of timestamps appended to  $\Gamma_r^{\mathcal{U}}$  and  $\Gamma_c^{\mathcal{U}}$  signifies that there is a new valid interval where the constraint,  $\psi_1 \mathcal{U}_{[a,b]}\psi_2$ , was met. As depicted in the *Until* example in Figure 2.b, we have  $t_{r_1}^{\mathcal{U}} = max(1,2-4) = 1$  and  $t_{f_1}^{\mathcal{U}} = min(5,9)-2 =$ 3. Since  $t_{r_1}^{\mathcal{U}} < t_{f_1}^{\mathcal{U}}$  they can be used to update  $\psi_1 \mathcal{U}_{[2,4]} \psi_2$  by being

$<sup>{}^{1}\!\</sup>uparrow\psi=(\psi\wedge(\neg\psi\,\mathcal{S}T))\vee(\neg\psi\wedge(\psi\,\mathcal{U}T))\text{ for rising edges and }$

$<sup>\</sup>downarrow \psi = (\neg \psi \land (\psi ST)) \lor (\psi \land (\neg \psi UT)) \text{ for falling edge.}$

DAC'18, July 2018, San Francisco, California, USA

Algorithm 2 Eventually  $(t_r^{\psi}, t_f^{\psi}, \mathbf{a}, \mathbf{b})$ 1:  $t_{r_i}^{\Diamond} = t_r^{\psi} - b$ 2:  $t_{f_i}^{\Diamond} = t_f^{\psi} - a$ 3: if  $t_{r_i}^{\Diamond} < 0$  then 4:  $t_{r_i}^{\Diamond} = 0$ 5: end if 6: if  $t_{f_{i-1}}^{\Diamond} < t_{r_i}^{\Diamond}$  then 7:  $\Gamma_r^{\Diamond} = \Gamma_r^{\Diamond} + \{t_{r_i}^{\Diamond}\}$ 8:  $\Gamma_f^{\Diamond} = \Gamma_f^{\Diamond} + \{t_{f_i}^{\Diamond}\}$ 9: end if 10: if  $t_{r_i}^{\Diamond} < = t_{f_{i-1}}^{\Diamond}$  and  $t_{f_{i-1}}^{\Diamond} < t_{f_i}^{\Diamond}$  then 11:  $\Gamma_f^{\Diamond} = \Gamma_f^{\Diamond} - \{t_{f_{i-1}}^{\Diamond}\}$ 12:  $\Gamma_f^{\Diamond} = \Gamma_f^{\Diamond} + \{t_{f_i}^{\Diamond}\}$ 13: end if

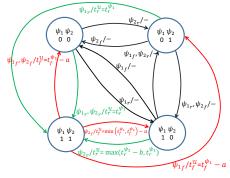

appended to  $\Gamma_r^{\mathcal{U}}$  and  $\Gamma_f^{\mathcal{U}}$ . The potential  $\psi_1 \mathcal{U}_{[2,4]} \psi_2$  rising and falling edges obtained from the second pulse of  $\psi_1$  are then computed as follows:  $t_{r_2}^{\mathcal{U}} = max(7, 2 - 4) = 7$  and  $t_{f_2}^{\mathcal{U}} = min(8, 9) - 2 = 6$ . Since  $t_{f_2}^{\mathcal{U}} \leq t_{r_2}^{\mathcal{U}}$  they must be disregarded rather than appended to  $\Gamma_r^{\mathcal{U}}$ and  $\Gamma_f^{\mathcal{U}}$ . This concludes that  $\mathcal{U}_{[2,4]}$ , were met in the interval from time t = 1 to t = 3, when the first pulse of  $\psi_1$  must hold until the rising event on  $\psi_2$  is true at some time step between a and  $b^2$ . The Finite State Machine (FSM) in Figure 3, calculates the result of Untiloperator with just four states (two bits)<sup>3</sup>.

$\overline{ Algorithm 3 \text{ Until } (t_r^{\psi_1}, t_r^{\psi_2}, t_f^{\psi_1}, t_f^{\psi_2}, a, b) }$   $1: t_{r_i}^{\mathcal{U}} = max(t_r^{\psi_1}, t_r^{\psi_2} - b)$   $2: t_{f_i}^{\mathcal{U}} = min(t_f^{\psi_1}, t_f^{\psi_2}) - a$   $3: \text{ if } t_{r_i}^{\mathcal{U}} < 0 \text{ then}$   $4: t_{r_i}^{\mathcal{U}} = 0$  5: end if  $6: \text{ if } t_{f_{i-1}}^{\mathcal{U}} < t_{r_i}^{\mathcal{U}} \text{ and } t_{r_i}^{\mathcal{U}} < t_{f_i}^{\mathcal{U}} \text{ then}$   $7: \Gamma_r^{\mathcal{U}} = \Gamma_r^{\mathcal{U}} + \{t_{r_i}^{\mathcal{U}}\}$   $8: \Gamma_f^{\mathcal{U}} = \Gamma_f^{\mathcal{U}} + \{t_{f_i}^{\mathcal{U}}\}$  9: end if  $10: \text{ if } t_{r_i}^{\mathcal{U}} < t_{f_i}^{\mathcal{U}} \text{ and } t_{f_{i-1}}^{\mathcal{U}} < t_{f_i}^{\mathcal{U}} \text{ then}$   $11: \Gamma_f^{\mathcal{U}} = \Gamma_f^{\mathcal{U}} - \{t_{f_{i-1}}^{\mathcal{U}}\}$   $12: \Gamma_f^{\mathcal{U}} = \Gamma_f^{\mathcal{U}} + \{t_{f_i}^{\mathcal{U}}\}$  13: end if

## 3.2 Event-based Approach

The second category of operators in TTL is event-based. They deal with timestamps of events ( $\Theta$  set) and produce boolean signals represented by rising and falling sets ( $\Gamma_r$  and  $\Gamma_f$ ).

Figure 3: FSM to implement an *Until* operator. FSM captures rise and fall time of boolean signals  $\psi_1$ ,  $\psi_2$  and computes  $\mathcal{U}$ .

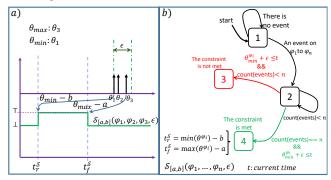

3.2.1 Simultaneity Constraint. To determine the satisfiability of the Simultaneity constraint, the point in time where a set of events have occurred within a time tolerance of  $\epsilon$  is evaluated. Figure 4.a shows the example of three events occurring within  $\epsilon$  so that the constraint is met between  $\theta_{min} - b$  and  $\theta_{max} - a$ . We use timed-automata to evaluate this timing constraint. As Figure 4.b, if the timed-automata detects *n* events and  $\epsilon$  duration passed after observing the first event the constraint can be calculated.

Figure 4: a) Calculation of *Simultaneity* constraint b) The timed-automata to calculate Simultaneity constraint.

3.2.2 Latency Constraint. A latency constraint specifies the time difference between the occurrence of two events. A simple example of a latency constraint is the minimum, maximum or exact time interval between two events, denoted as follows:  $\mathcal{L}(\varphi_1, \varphi_2) \, \nabla c$  where  $\nabla \in \{>, <, ==\}$ . The test code generation takes as input two events ( $\varphi_1$  and  $\varphi_2$ ) and compares the difference between the event timestamps with a real number *c*. Since the signals are singletons, the sets of  $\Theta^{\varphi_1}$  and  $\Theta^{\varphi_2}$  each contain one element. Hence, whenever event  $\Theta^{\varphi_2}$  is received, the latency can be calculated. The latency constraint evaluation is comprised of two steps: (1) calculating the delay  $\Delta t$  between two timestamps,  $\theta_1^{\varphi_1}$ , and  $\theta_1^{\varphi_2}$ , and (2) comparing  $\Delta t$  with *c*. Latency block,  $\Delta t = \theta_1^{\varphi_2} - \theta_1^{\varphi_1}$  in comparison block if  $((\Delta t \, \nabla c) == \top)$  then the rising and falling edges of result are:  $t_r^{\mathcal{L}} = \theta_1^{\varphi_2} - b$ ,  $t_f^{\mathcal{L}} = \theta_1^{\varphi_1} - a$ .

## 4 EMPIRICAL EVALUATION

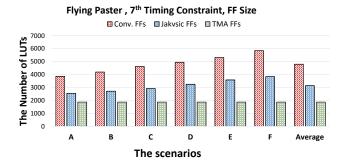

In this section, we applied TMA method to monitor timing constraints in Flying Paster application and compared the required number of FFs and LUTs with the *Counters* algorithm in [11]. Also, we implemented *Globally* operator with different time intervals to show the required memory for an FPGA implementation (Table 1).

M. Mehrabian et al.

<sup>&</sup>lt;sup>2</sup>In the calculations for  $\psi_1 \mathcal{U}_{[a,b]} \psi_2$  operator, we just consider the overlapped pulses on  $\psi_1$  and  $\psi_2$ .

<sup>&</sup>lt;sup>3</sup>The reader can find all proofs in https://github.com/cmlasu/tma. This link also contain a simulation software, *TMA\_Testing.zip*, to evaluate TTL timing constraints.

An Efficient Timestamp-Based Monitoring Approach to Test Timing Constraints of Cyber-Physical Systems

#### Table 1: Memory requirement on FPGA for Globally.

|   |                      | #FFs        |      | #LUTs       |      |  |

|---|----------------------|-------------|------|-------------|------|--|

|   |                      | Jakšić [11] | TMA  | Jakšić [11] | TMA  |  |

| 1 | [0,100]              | 1902        |      | 2981        |      |  |

| 2 | [0,200]              | 3935        |      | 5895        |      |  |

| 3 | [0,300]              | 7821        | 1820 | 9314        | 2696 |  |

| 4 | D[100,200]           | 1891        | 1020 | 2875        | 2090 |  |

| 5 | [200, 400]           | 3702        |      | 5431        |      |  |

| 6 | <sup>[300,600]</sup> | 6312        |      | 9612        |      |  |

## 4.1 Case Study: Flying Paster Application

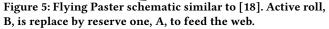

The schematic diagram of Flying Paster application [18, 19] is shown in Figure 5. The active roll B feeds the paper and should make contact with the reserve roll A before B runs out of paper, for continuous operations. C and E are idler wheels. Sensor H measures the radius of the paper on B and whenever the radius is less than a threshold, it generates an Approaching Out of Paper (AOP) event. Then, roll A starts to rotate. On the outer side of the reserve roll paper, there is a double-sided adhesive *tape*, which can be detected by sensors F and G. To calculate the angular velocity of roll A, sensors F and J are utilized. When the velocity of the paper at the edge of A becomes the same as roll B. *match* signal is generated. Once *match* is observed, after detecting two rotations, G can detect the tape. When G detects it, idler wheel E pushes the belt to the spare roll A, such that after tapeToContactAngle, papers on A and B attach together by the adhesive tape and then the paper on roll A follows the path. Cutter D should cut the paper on roll B after tapeToCutAngle. In order to ensure that the new paper is attached properly, we should have *tapeToContactAngle < tapeToCutAngle*.

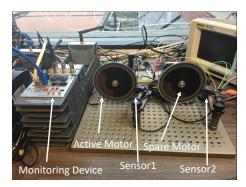

To implement this application, we used two Hansen DC motors as rolls A and B. Motors are driven by an Arduino Mega2560 board to control the speed and also to generate *AOP*, *match*, *contact* and *cut* signals. On each motor, we installed a dialed disk with a drilled hole at zero degree (Figure 6). An Omron EESX970C1 sensor was installed close to each disk to detect the drilled hole and hence, measure the rotation speed of each motor. We utilized an NI-cRIO 9035 with an on-board FPGA, Xilinx Kintex-7 7K70T, containing 82,000 FFs and 41,000 LUTs with a 40 MHz clock frequency. For signal monitoring, we used a 20 kHz NI-9381 I/O module and it uses a 12-bit ADC. The pins of NI-9381 were directly connected to *photomicrosensors*, *AOP*, *match*, *cut* and *contact* signals.

Next, we express timing constraints of flying paster application based on STL. The notations for the case study variables are as follows: linear velocity (V), radius (r) and angular velocity ( $\omega$ ). 1) The velocity of the paper on active roll should be constant:

$$V_{active} = (r_{active} \times \omega_{active}) \pm 1\%$$

m/s

#### DAC'18, July 2018, San Francisco, California, USA

Figure 6: Implemented Flying paster comprises 2 motors and is monitored by reconfigurable data acquisition system.

$\Box_{[t_i, t_s]}(V_{active} = r_{active} \times \omega_{active} \pm 1\%)$ 2) The time interval between *AOP* rising to *match* rising edge must be no more than  $t_{action}$ :  $\Box(\uparrow AOP \Rightarrow \diamondsuit_{[0, t_{action}]}(\uparrow match))$ 3) After *match*, the paper speed of the spare should remain the same as active:  $V_{active} = r_{active} \times \omega_{active}$  and  $V_{spare} = V_{active} \pm 1\%$

$\Box_{[t_{match}, t_{cut}]}(V_{active} = r_{active} \times \omega_{active})$  $\Box_{[t_{match}, t_{cut}]}(V_{spare} = r_{spare} \times \omega_{spare})$  $\Box_{[t_{match}, t_{cut}]}(V_{spare} = V_{active} \pm 1\%)$

4) Catch the *TDC* (2 rotations of A after *match*).

$$t_{spareTDC} - t_{matchOnSpare} < \frac{4\pi}{\omega_{spare}}$$

$$\diamond_{[t_{match}, t_{match} + \frac{4\pi}{\omega_{spare}}]}(\uparrow spareTDC)$$

5) When tape is 225 degrees after G, contact signal must fire.

$$t_{contact} - (t_{spareTDC} + \frac{225 \ degrees}{\omega_{spare}}) < \pm 1 \ ms$$

$\Box_{[t_{spareTDC} + \frac{225 \ degrees}{\omega_{spare} + 1 \ ms}, t_{spareTDC} + \frac{225 \ degrees}{\omega_{spare} - 1 \ ms}](\uparrow \ contact)}$ 6) When tape is 270 degrees after G, *cut* signal must fire.

$t_{cut} - (t_{spareTDC} + \frac{270 \ degrees}{2}) < \pm 1 \ ms$

$$\Box_{[t_{spareTDC} + \frac{270 \ degrees}{\omega_{spare1} \ ms}, t_{spareTDC} + \frac{290 \ degrees}{w_{spare1} \ ms}]}(\uparrow cut)$$

7)

$(\uparrow cut)$

We implemented the timing constraints of Flying Paster with three approaches (conventional, Jakšić [11] and TMA) on FPGA.

4.1.1 Temporal Logic Expression. We began with the conventional method describing the constraints in STL. We changed the future STL formulas to the past ones [11], and we represented the same timing constraint in TTL for TMA. For example, in  $\Box(\uparrow AOP \Rightarrow \diamond_{[0, t_{action}]}(\uparrow match))$ , we have:

1) Conventional Method (which is pointed out as *Register Buffer* in [11]): Since rising and falling edges ( $\uparrow$  and  $\downarrow$ ) cannot be represented in STL, we express them as the way in [17]:

$$\uparrow \psi = (\psi \land (\neg \psi \ S \ T)) \lor (\neg \psi \land (\psi \ U \ T)) \downarrow \psi = (\neg \psi \land (\psi \ S \ T)) \lor (\psi \land (\neg \psi \ U \ T))$$

Therefore, the example is converted to:

$\Box((AOP \land (\neg AOP \ \mathcal{S} \ T)) \lor (\neg AOP \land (AOP \ \mathcal{U} \ T)) \Rightarrow$

$\diamond_{[0, t_{action}]}(match \land (\neg match S T) \lor (\neg match \land (match U T)))$ 2) Jakšić in [11] method: Future STL should be converted into past:

$\Box(\diamondsuit_{\{t_{action}\}} \uparrow AOP \Rightarrow \diamondsuit_{[0, t_{action}]}(\uparrow match))$

The edge  $(\uparrow)$  operator should be replaced by the equivalent constraint like the conventional method.

#### DAC'18, July 2018, San Francisco, California, USA

Flying Paster Timing Constraints, FF and LUT size ☑ Jaksic LUTs ■ TMA FFs ◎ TMA LUTs Conv. Could not Both Could not Conv.FF: Conv. LUTs S Jaksic FFs 80% FLIP-FLOP SIZE(PERCENTAGE) 70% be compiled be compiled 60% 50% 40% 30% 20% 10% 0% C D THE SCENARIOS

#### Figure 7: Comparison of FF and LUT numbers in 3 methods.

3) TMA method: Since the constraint is a latency between *AOP* and *match*, it can be easily written in TTL as:

$\mathcal{L}(\langle AOP, 2.5 V, \nearrow \rangle, \langle match, 2.5 V, \nearrow \rangle) \leq t_{action}$

The level threshold, 2.5 V, is the threshold to detect *true* or *false* on the boolean signal (0 V and 5 V correspond to *false* and *true*, respectively). Next, we implemented the constraint specifications on the FPGA using the three monitoring methods.

Table 2: Six different scenarios in which the linear speed of active roll, *AOP* to *match* and time to *contact* time are varied.

|                          | A      | В      | С      | D      | E      | F      |

|--------------------------|--------|--------|--------|--------|--------|--------|

| vactive                  | 22 m/s | 20 m/s | 18 m/s | 16 m/s | 14 m/s | 12 m/s |

| taction                  | 2 s    | 3 s    | 4 s    | 5 s    | 6 s    | 7 s    |

| t <sub>termination</sub> | 3 s    | 4 s    | 5 s    | 6 s    | 7 s    | 8 s    |

As Figure 7 depicts, conventional and Jakšić methods required more FFs and LUTs in the case study. With increasing intervals, the FF and LUT utilization increases linearly for the Jakšić method. In  $\Leftrightarrow_{[a,b]} \psi = \Leftrightarrow_{\{a\}} \Leftrightarrow_{[a,b-a]}$ , the variability is b - a + 1. In contrast, TMA takes a constant amount of memory in all scenarios because it does not require retention of signal history. When a signal event is observed, the result can be deduced. Moreover, the computation part – that affects the LUT size – is minimal by reducing operators (either event-based or level-based) to simple computations.

## 4.2 Low variability signals

We evaluate the last timing constraint of flying paster application  $(\diamond_{[t_{AOP}, t_{AOP}+t_{termination}]}(\uparrow cut))$ , using all three methods to see the efficiency of TMA in monitoring low variability signals for different values of  $t_{termination}$  as shown in the third row of Table 2. Figure 8 compares the FF utilization based upon the conventional, Jakšić, and TMA approaches for constraint evaluation in the case study application, where TMA used the least amount of memory.

Figure 8: #FFs utilization in three methods.

## 5 CONCLUSION

We propose a lightweight monitoring methodology, TMA, for CPS timing constraints and demonstrated the efficiencies gained based on an initial case study. The approach utilizes signal timestamps to compute the range for a constraint, rather than processing the levels of signals, requiring data at each sample. The proposed method minimizes computation overhead compared to existing monitoring approaches. The implementation is independent of the constraint interval, allowing the memory usage to be constant for any interval. TMA is particularly geared towards monitoring constraints in TTL, which allows for the succinct description of common timing constraints in CPS, thus simplifying the description and the constraint evaluation algorithms. Future research in this area includes expansion of constraint primitives, such as duration, to fully capture and express temporal constraints in CPS.

**Disclaimer**: Certain commercial entities, equipment, or materials are identified in this document in order to describe the experimental design or to illustrate concepts. Such identification is not intended to imply recommendation or endorsement by the National Institute of Standards and Technology or the institutions of the other authors, nor is it intended to imply that the entities, materials, or equipment are necessarily the best available for the purpose.

#### REFERENCES

- Aviral Shrivastava et al. A Testbed to Verify the Timing Behavior of Cyber-Physical Systems. In DAC. ACM, 2017.

- [2] Oded Maler et al. Checking Temporal Properties of Discrete, Timed and Continuous Behaviors. LNCS, 2008.

- [3] Dejan Nickovic. Checking Timed and Hybrid Properties: Theory and Applications. PhD thesis, Université Joseph-Fourier-Grenoble I, 2008.

- [4] Thomas Reinbacher, Matthias Függer, and Jörg Brauer. Runtime Verification of Embedded Real-time Systems. Formal methods in system design, 2014.

- [5] Alexandre Donzé, Thomas Ferrere, and Oded Maler. Efficient Robust Monitoring for STL. In CAV. Springer, 2013.

- [6] Georgios E Fainekos and George J Pappas. Robustness of Temporal Logic Specifications. In FATES/RV. Springer, 2006.

- [7] Georgios E Fainekos and George J Pappas. Robustness of Temporal Logic Specifications for Continuous-time Signals. *Theoretical Computer Science*, 2009.

- [8] Georgios E Fainekos et al. Verification of Automotive Control Applications using S-Taliro. In American Control Conference (ACC). IEEE, 2012.

- [9] Howard Barringer, Allen Goldberg, Klaus Havelund, and Koushik Sen. Program Monitoring with LTL in EAGLE. In IPDPS. 18th. IEEE, 2004.

- [10] Jyotirmoy V Deshmukh et al. Robust online monitoring of signal temporal logic. In Runtime Verification, pages 55–70. Springer, 2015.

- [11] Stefan Jakšićet al. From Signal Temporal Logic to FPGA Monitors. In MEMOCODE, 2015.

- [12] Wang Mianet al. A Review on AC and DC Protection Equipment and Technologies: Towards Multivendor Solution. In CIGRE INTERNATIONAL COLLOQUIUM, 2017.

- [13] Mohammadreza Mehrabian *et al.* Timestamp Temporal Logic (TTL) for Testing the Timing of Cyber-Physical Systems. In *ESWEEK*. ACM, 2017.

- [14] Alexandre Donzé. Breach, A Toolbox for Verification and Parameter Synthesis of Hybrid Systems. In CAV, volume 10, pages 167–170. Springer, 2010.

- [15] Yashwanth Annpureddy et al. S-TaLiRo: A Tool for Temporal Logic Falsification for Hybrid Systems. In TACAS. Springer, 2011.

- [16] Dejan Nickovic and Oded Maler. AMT: A Property-based Monitoring Tool for Analog Systems. Formal Modeling and Analysis of Timed Systems, 2007.

- [17] Oded Maler and Dejan Ničković. Monitoring Properties of Analog and Mixedsignal Circuits. STTT, 2013.

- [18] Patricia Derler et al. Using PTIDES and Synchronized Clocks to Design Distributed Systems with Deterministic System Wide Timing. In ISPCS. IEEE, 2013.

- [19] Drupaloge. PrintIP Lithoman IV flying splice, last accessed nov. 2017. URL https://www.youtube.com/watch?NR=1%5C&v=wYRGiXMUzA4.