# WCET-Aware Scratchpad Memory Management for Hard Real-Time Systems

by

Yooseong Kim

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved December 2016 by the Graduate Supervisory Committee:

Aviral Shrivastava, Chair David Broman Georgios Fainekos Carole-Jean Wu

ARIZONA STATE UNIVERSITY

May 2017

#### **ABSTRACT**

Cyber-physical systems and hard real-time systems have strict timing constraints that specify deadlines until which tasks must finish their execution. Missing a deadline can cause unexpected outcome or endanger human lives in safety-critical applications, such as automotive or aeronautical systems. It is, therefore, of utmost importance to obtain and optimize a safe upper bound of each task's execution time or the worst-case execution time (WCET), to guarantee the absence of any missed deadline. Unfortunately, conventional microarchitectural components, such as caches and branch predictors, are only optimized for average-case performance and often make WCET analysis complicated and pessimistic. Caches especially have a large impact on the worst-case performance due to expensive offchip memory accesses involved in cache miss handling. In this regard, software-controlled scratchpad memories (SPMs) have become a promising alternative to caches. An SPM is a raw SRAM, controlled only by executing data movement instructions explicitly at runtime, and such explicit control facilitates static analyses to obtain safe and tight upper bounds of WCETs. SPM management techniques, used in compilers targeting an SPM-based processor, determine how to use a given SPM space by deciding where to insert data movement instructions and what operations to perform at those program locations. This dissertation presents several management techniques for program code and stack data, which aim to optimize the WCETs of a given program. The proposed code management techniques include optimal allocation algorithms and a polynomial-time heuristic for allocating functions to the SPM space, with or without the use of abstraction of SPM regions, and a heuristic for splitting functions into smaller partitions. The proposed stack data management technique, on the other hand, finds an optimal set of program locations to evict and restore stack frames to avoid stack overflows, when the call stack resides in a size-limited SPM. In the evaluation, the WCETs of various benchmarks including real-world automotive applications are statically calculated for SPMs and caches in several different memory configurations.

## Acknowledgement

My Ph.D. studies were truly a life changing experience. I first started with excitement and enthusiasm, but prolonged challenges with research and multifaceted life problems soon filled me with frustration and shame. Now I am finishing my 8 years of studies with great humility and gratitude. I would not have been able to finish, or even keep my sanity, without the help and support of many people. I wish I could present them this thesis as a masterpiece in a way to show my sincere gratitude, but I can only realize my limitations. I am afraid to thank everyone with mere words instead.

Prof. Aviral Shrivastava was the initiator and enabler of all these. He not only gave me opportunities to start the studies, but also sustained me and helped me go through myriads of problems and difficulties. I truly enjoyed working with him and learned from him a different kind of warm leadership that has patience and consistency in being constructive toward making progress. He always rescued me from self-hatred and lack of confidence and finally turned me into a proud student of him. He is my best advisor, mentor, teacher, researcher, and even a good friend and counsellor to me.

Meeting Prof. David Broman was a turning point in my life. He opened my eyes to research with the depth and gravitas that I had not even realized. I will cherish the rewarding discussions and the memories during the time at UC Berkeley. I learned from him invaluable lessons about the researcher's responsibility and ethics, and also perfectionism. It is with my regret that I could and might have done better to make this relationship more fruitful. I would like to sincerely thank Prof. David Broman for all his support and help.

Without the valuable inspiration and advice from Prof. Georgios Fainekos and Prof. Carole-Jean Wu, I would not have been able to finish this thesis. Having them in my committee broadened my view of the problem, and I could significantly improve this thesis

with their valuable comments and suggestions, from the early stage of this work at thesis proposal to the final stage of thesis defense.

During the most time of my Ph.D. studies, I lived in California, away from campus, working remotely. Because of the difficulties and lonesomeness I experienced during this time, I truly understand the value our comradeship and friendship. Each and every conversation and discussion, short or long, with fellow graduate students helped me get through difficulties at the moment and gave me a new lesson. I would especially like to thank all past and current members of Compiler-Microarchitecture Lab and Korean Student Fellowship in CS department.

I would like to show my deepest gratitude to my wife Soyoun. Without her love, support, encouragement, and endurance, I would never have been able to hold out until this very moment. Also, without my dear daughter Olivia, I could not have realized the truth of life and the value of family. I am grateful to have this wonderful family in my life and to be able to start a new chapter of our life together as family. Last but not least, I would like to thank God for sustaining me so far and for His countless blessings. I trust in the Lord, who is my good shepherd, and would like to declare that the sovereign God is in control of all things in my life and the world.

# TABLE OF CONTENTS

|      |       |           |                                                       | Page |

|------|-------|-----------|-------------------------------------------------------|------|

| LIST | OF TA | ABLES     |                                                       | vii  |

| LIST | OF FI | GURES .   |                                                       | viii |

| CHAI | PTER  |           |                                                       |      |

| 1    | INT   | RODUCTI   | ION                                                   | 1    |

|      | 1.1   | Scratchpa | ad Memory (SPM) and Its Management                    | 3    |

|      | 1.2   | Overview  | of This Thesis                                        | 6    |

|      | 1.3   | Contribut | tions                                                 | 7    |

|      | 1.4   | Related F | Publications                                          | 8    |

| 2    | WCI   | ET-AWAR   | E FUNCTION-LEVEL DYNAMIC CODE MANAGEMENT .            | 9    |

|      | 2.1   | Introduct | ion                                                   | 9    |

|      | 2.2   | Backgrou  | and: Function-level Dynamic Code Management           | 11   |

|      | 2.3   | Motivatir | ng Examples                                           | 12   |

|      |       | 2.3.1 V   | Why Do We Need a New Technique for Optimizing WCET?   | 13   |

|      |       | 2.3.2 V   | Why Do We Need Region-Free Mapping?                   | 14   |

|      | 2.4   | WCET A    | nalysis                                               | 15   |

|      |       | 2.4.1 In  | nlined Control Flow Graph                             | 16   |

|      |       | 2.4.2 F   | inding Initial Loading Points                         | 18   |

|      |       | 2.4.3 F   | inding the Interference among Functions               | 18   |

|      |       | 2.4.4 II  | LP Formulation for WCET Analysis                      | 22   |

|      | 2.5   | WCET O    | ptimization                                           | 25   |

|      |       | 2.5.1 II  | LP Formulation for Optimal Function-to-region Mapping | 25   |

|      |       | 2.5.2 V   | WMP: A Heuristic Alternative to the ILP Formulation   | 27   |

|      |       | 2.5.3 C   | Optimizing WCET using Region-free Mappings            | 33   |

|      | 2.6   | Experime  | ental Results                                         | 35   |

| CHAPT | ΓER  |         |                                                      | Page |

|-------|------|---------|------------------------------------------------------|------|

|       |      | 2.6.1   | ILP vs. WMP Heuristic                                | . 38 |

|       |      | 2.6.2   | Comparison with Previous Techniques                  | . 40 |

|       |      | 2.6.3   | Function-to-region Mappings vs. Region-free Mappings | . 42 |

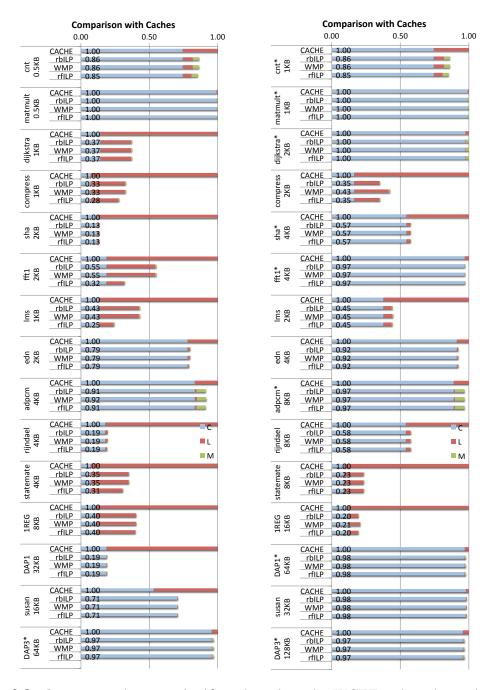

|       |      | 2.6.4   | WCET Reduction over Caches                           | . 44 |

| ,     | 2.7  | Relate  | d Work                                               | . 47 |

| ,     | 2.8  | Summ    | ary                                                  | . 50 |

| 3 .   | A CO | OMPAR   | RISON OF DYNAMIC CODE MANAGEMENT TECHNIQUES          |      |

|       | WIT  | H DIFF  | FERENT MANAGEMENT GRANULARITIES                      | . 52 |

|       | 3.1  | Introdu | uction                                               | . 52 |

|       | 3.2  | Relate  | d Work                                               | . 55 |

|       | 3.3  | Dynan   | nic Code Management Techniques                       | . 58 |

|       |      | 3.3.1   | BL: Basic-block-level Approach                       | . 58 |

|       |      | 3.3.2   | FL: Function-level Approach                          | . 62 |

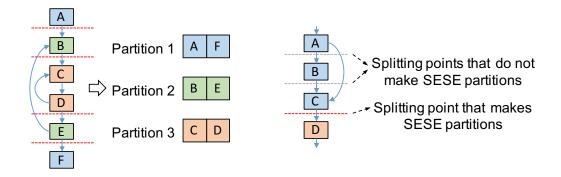

|       |      | 3.3.3   | RL: Splitting Functions into Partitions              | . 63 |

|       | 3.4  | Qualita | ative Comparison                                     | . 67 |

|       |      | 3.4.1   | WCET Analysis                                        | . 67 |

|       |      | 3.4.2   | SPM Size Limitations                                 | . 68 |

|       |      | 3.4.3   | Management Efficiency                                | . 69 |

|       | 3.5  | WCET    | G-Based Quantitative Comparison                      | . 71 |

|       |      | 3.5.1   | Experimental Setup                                   | . 72 |

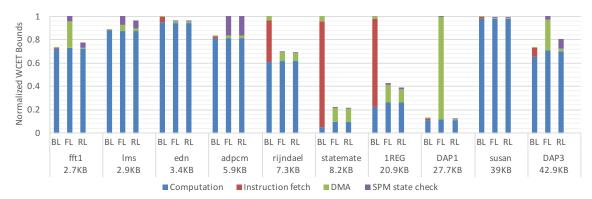

|       |      | 3.5.2   | Baseline Results                                     | . 75 |

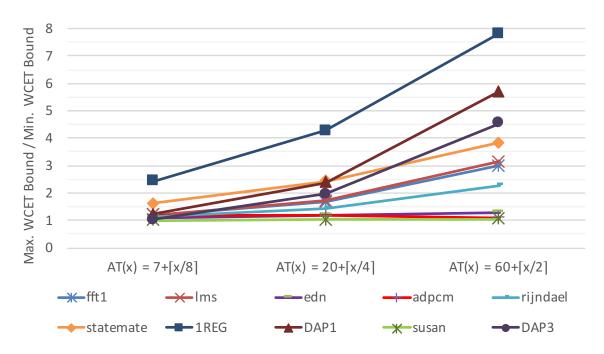

|       |      | 3.5.3   | Changing Memory Sizes                                | . 77 |

|       |      | 3.5.4   | Changing Memory Access Times                         | . 78 |

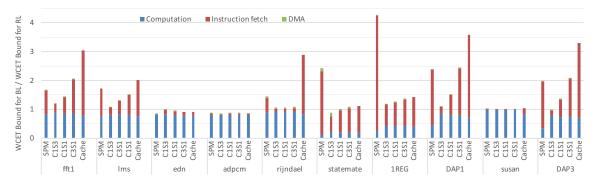

|       |      | 3.5.5   | Changing Memory Organizations with Caches            | . 79 |

| CHAPTER  | Pa                                         | ige |

|----------|--------------------------------------------|-----|

| 3.6      | Summary and Conclusion                     | 81  |

| 4 WC     | ET-AWARE DYNAMIC STACK FRAME MANAGEMENT    | 84  |

| 4.1      | Introduction                               | 84  |

| 4.2      | Related Work                               | 85  |

| 4.3      | Background: Dynamic Stack Frame Management | 88  |

|          | 4.3.1 Limitations                          | 90  |

| 4.4      | WCET-Aware Dynamic Stack Frame Management  | 90  |

|          | 4.4.1 ILP Formulation                      | 91  |

|          | 4.4.2 Example                              | 94  |

| 4.5      | Evaluation                                 | 95  |

|          | 4.5.1 Comparison with Previous Techniques  | 96  |

|          | 4.5.2 Comparison with Caches               | 98  |

| 4.6      | Summary                                    | 99  |

| 5 CON    | ICLUSION AND FUTURE WORK                   | 00  |

| REFEREN  | CES                                        | 02  |

| APPENDIX |                                            |     |

| A CAC    | CHE ANALYSIS 1                             | 11  |

# LIST OF TABLES

| Table |                                                                  | Page |

|-------|------------------------------------------------------------------|------|

| 2.1   | Interference Sets for the Example in Figure 2.4                  | . 20 |

| 2.2   | Categorization of Function Loading Cost                          | . 24 |

| 2.3   | Benchmarks Used in the Evaluation                                | . 36 |

| 2.4   | Execution Time Comparison between ILP and WMP Heuristic          | . 39 |

| 3.1   | Categorization of Code Management Techniques Based on Management |      |

|       | Granularity                                                      | . 53 |

| 3.2   | Benchmarks Used in the Evaluation                                | . 71 |

# LIST OF FIGURES

| Fig | ure  | 1                                                                | Page |

|-----|------|------------------------------------------------------------------|------|

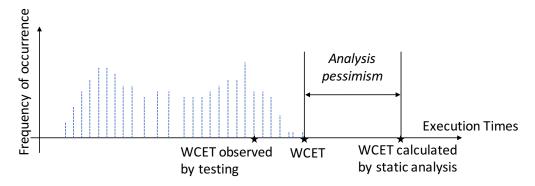

|     | 1.1  | The Basics of Worst-case Execution Time Analysis                 | 2    |

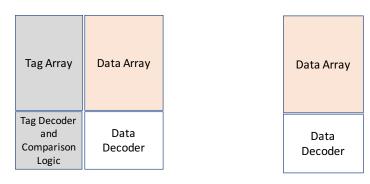

|     | 1.2  | Hardware Organization of Scratchpad Memory                       | 3    |

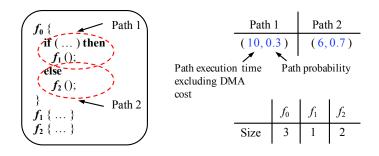

|     | 2.1  | Motivation for WCET-optimizing Code Management Technique         | 12   |

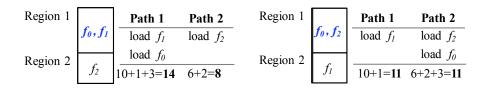

|     | 2.2  | Motivation for Region-Free Mapping                               | 15   |

|     | 2.3  | Overview of WCET Analysis for Code Management                    | 16   |

|     | 2.4  | Inlined CFG.                                                     | 17   |

|     | 2.5  | Comparison Between the ILP and WMP Heuristic                     | 38   |

|     | 2.6  | Comparison with Previous Function-Level Techniques               | 41   |

|     | 2.7  | WCET Reduction by Region-free Mapping                            | 42   |

|     | 2.8  | Comparison with Caches                                           | 45   |

|     | 3.1  | A Problem with Loop Handling in Basic-block-level Techniques     | 61   |

|     | 3.2  | An Illustrative Implementation of Function-Level Code Management | 62   |

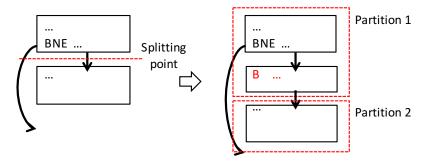

|     | 3.3  | An Illustration of Our Function-Splitting Scheme                 | 65   |

|     | 3.4  | Code Modification for a Fall-Through Branch                      | 66   |

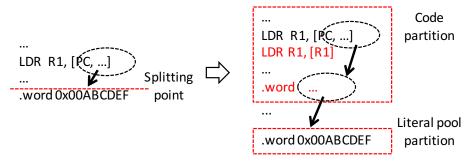

|     | 3.5  | Code Modification for a Literal Access                           | 67   |

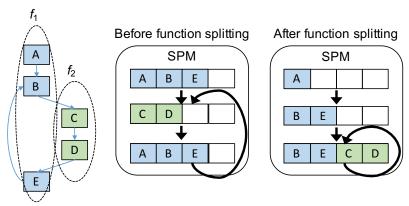

|     | 3.6  | An Example of Function Splitting                                 | 70   |

|     | 3.7  | Baseline Results                                                 | 74   |

|     | 3.8  | Results for Larger SPM Sizes                                     | 77   |

|     | 3.9  | Results for Different Memory Access Times                        | 78   |

|     | 3.10 | Results for Different Memory Organizations                       | 80   |

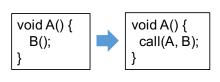

|     | 4.1  | Code Modification for Stack Frame Management                     | 88   |

|     | 4.2  | An Illustration of Stack Frame Management                        | 89   |

|     | 4.3  | A simple inlined CFG used as an example                          | 94   |

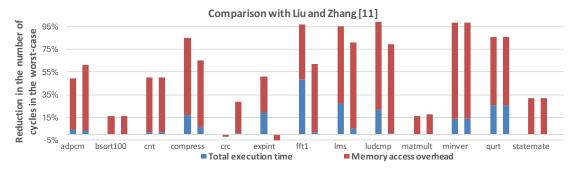

|     | 4.4  | Comparison with Liu and Zhang (2015)                             | 97   |

| Figure |                                  | Page |

|--------|----------------------------------|------|

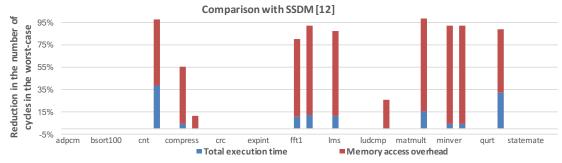

| 4.5    | Comparison with Lu et al. (2013) | 97   |

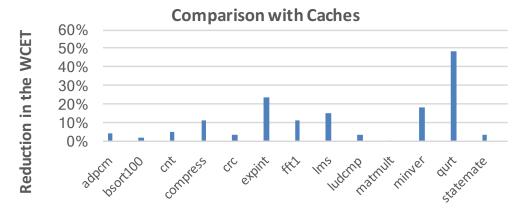

| 4.6    | Comparison with Caches           | 98   |

### Chapter 1

#### INTRODUCTION

Hard real-time systems (Buttazzo, 2011) or cyber-physical systems (Lee, 2008) are subject to strict timing constraints that require tasks to finish execution before their specified *dead-lines*. Any failure to meet a timing constraint can lead to unexpected outcomes, thus timing is a key factor in functional correctness, not only a performance measure in these systems. Particularly, in safety-critical applications, such as automobiles or aircrafts, a missed deadline may cause devastating and even life-threatening consequences. It is, therefore, of utmost importance to guarantee that all timing constraints are satisfied.

To check the presence of missed deadlines, testing has been widely used as a traditional approach in industry in the context of system validation. It is, however, very difficult to cover all possible test cases and to identify representative worst-cases. The sheer number of test cases in modern real-time systems makes exhaustive testing infeasible. Moreover, it is often difficult to identify the execution scenarios that lead to the worst-case execution times (WCETs) of tasks. These worst-case scenarios are often counterintuitive due to timing anomalies (Reineke *et al.*, 2006; Lundqvist and Stenström, 1999), commonly present in highly-optimized modern real-time systems. It is not possible to guarantee that the actual WCETs have been observed in testing, and therefore testing is not a safe way of validating timing correctness of hard real-time systems.

The absence of missed deadlines can only be guaranteed by a static analysis (Wilhelm *et al.*, 2008). A static WCET analysis estimates or calculates a *safe upper bound* of the WCETs of each task without actually executing them. As these estimates are safe upper bounds, a system that is validated using a static analysis is guaranteed to have timing correctness at any circumstances.

**Figure 1.1:** Worst-case execution time (WCET) observed by testing may not be the actual WCET, and only by static analyses, we can obtain a safe upper bound of the WCET. The pessimism in the analysis can, however, limit the practical usability of the results.

Although the safety of the results is not of critical importance here, the practical usability of an analysis can be limited because of the tightness of its results. Figure 1.1 illustrates the tightness of the results or pessimism in the analysis, as the gap between the actual WCET and the calculated WCET. For example, assuming a cache miss for every memory access is certainly a safe way to estimate the worst-case memory access times, but it can be so pessimistic that tasks may not be scheduled without significantly upgrading system hardware or changing the design. The tightness of the analysis results are largely affected by the timing predictability (Schoeberl, 2012) of the target processor architecture <sup>1</sup>. Unfortunately, traditional approaches for improving the average-case performance, e.g. caches and speculative execution, often complicate static analyses and make results pessimistic (Axer et al., 2014).

In particular, caches are difficult to analyze statically, and an imprecise cache analysis is an important source of pessimism (Reineke, 2009; Cazorla *et al.*, 2013). The contents of a cache during the execution of a task depend on previous execution history, so all execution

<sup>&</sup>lt;sup>1</sup> The uncertainties in software, such as unknown loop bounds, recursion depths or pointer values, have a critical impact on the timing predictability, too. They can, however, be controlled and reduced by code annotations and strict coding guidelines. For instance, safety standards for avionics (Radio Technical Commission for Aeronautics Special Committee (152), 1992) or coding guidelines for safety-critical systems (Montgomery, 2013) forbid or strictly limit the usage of recursion or dynamic memory allocation.

(a) Cache (b) Scratchpad Memory (SPM)

**Figure 1.2:** Scratchpad memories are a directly-addressable raw memory whose data movement is controlled only by software, not by hardware logic as in caches.

paths of the task and all higher-priority tasks including interrupt service routines must be analyzed, which is quite computationally intensive. Notice that for shared caches, all tasks running on all cores must be considered as well. In the presence of sporadic preemptions or under dynamic scheduling policies, accurately predicting the dynamic behavior of caches is nearly impossible because it is not clear when preemptions occur by which tasks. Thus, caches are not as effective in improving worst-case performance as they are in average-case performance. As the complexity and the size of hard real-time applications keep increasing, the difficulties in cache analysis can become a stumble stone in designing correctness-guaranteed hard real-time systems.

#### 1.1 Scratchpad Memory (SPM) and Its Management

Scratchpad memories (SPMs) are a promising alternative to caches in hard real-time systems, for their time-predictable characteristics. SPM is a raw memory that is directly addressable by software. Its simpler hardware, as shown in Figure 1.2, provides less overhead than caches in terms of die area and and per-access power consumption (Banakar et al., 2002a; Redd et al., 2014), which is much appreciated in embedded systems. Data movement in an SPM is explicitly controlled only by executing direct memory access (DMA) instructions whereas that in a cache is implicitly controlled by the addresses of

memory accesses and its replacement policy. Since the updates in the contents are made explicitly, SPMs are more time-predictable and thus facilitate static analyses (Suhendra et al., 2005; Liu et al., 2012). Also, explicit management enables various optimizations in a form of memory space allocation and access scheduling to reduce the WCETs. One key strategy, for example, to optimize the WCET of a task is to avoid memory space sharing among software objects frequently accessed on the worst-case execution path of the task. Moreover, partitioning SPM space to tasks and interrupt service routines can greatly simplify schedulability analysis that calculates the worst-case response times (WCRTs) based on the WCETs and scheduling policy in use. If the memory accesses from each task are completely localized to its partition, preemptions or interrupts do not cause any side effects on the SPM states. This means that cache-related preemption delay (CRPD) analysis (Altmeyer et al., 2011; Chattopadhyay and Roychoudhury, 2014; Altmeyer and Burguière, 2011), which tend to be pessimistic, can be completely removed in the design process. Of course, cache locking (Plazar et al., 2012; Ding et al., 2014) and partitioning (Liu et al., 2010; Suhendra and Mitra, 2008) can be used to lower WCETs by reducing conflict misses, but the granularity of these techniques is limited by blocks, lines or ways, which may cause a waste of cache space (Whitham and Audsley, 2009). Link-time optimizations such as code positioning techniques can be used to avoid conflict misses among instructions of different functions and reduce WCETs (Falk and Kotthaus, 2011; Um and Kim, 2003; Li et al., 2015), but the amount of reduction is not significant because these techniques are again, limited by the degree of control provided by caches; for example, line sizes and associativity cannot be changed.

Using an SPM requires a modification in a program; explicit data movement instructions need to be inserted into the program. This modification is usually done by a compiler. Before a compiler performs such a code transform, it needs to make number of decisions. It first needs to decide where in the code to insert a data movement operation. And for each

data movement operation, it needs to decide what to transfer from where and to where. The vast literature on SPM management techniques answers these questions in one way or another with different goals. As techniques to be used in a compiler, they typically employ static analysis and try to optimize reducing power consumptions (Steinke *et al.*, 2002a; Verma *et al.*, 2004; Steinke *et al.*, 2002b), improving average-case performance (Kandemir and Choudhary, 2002; Jung *et al.*, 2010; Bai *et al.*, 2013; Egger *et al.*, 2006; Pabalkar *et al.*, 2008; Baker *et al.*, 2010; Lu *et al.*, 2013; Nguyen *et al.*, 2009; Udayakumaran *et al.*, 2006; Avissar *et al.*, 2002), or worst-case performance (Falk and Kleinsorge, 2009; Puaut and Pais, 2007; Wu *et al.*, 2010; Prakash and Patel, 2012; Suhendra *et al.*, 2005; Wan *et al.*, 2012; Deverge and Puaut, 2007). In this thesis, we present present management techniques to reduce the WCET of a given program and particularly focus on the management of program code and stack data.

SPM management techniques can be either static or dynamic. Any usage of SPM creates a mapping between the main memory contents and the SPM contents. This applies to any on-chip memories; for example, the contents in a cache are a temporary copy or an alias of selected data in the main memory. This mapping between SPM addresses and main memory addresses can be one to one or one to many. In static management, it is one to one such that only selected data can make use of the SPM. The total size of data that can benefit of the SPM cannot be greater than the size of the SPM. For instance, when managing read-only data such as code, the selected instructions are loaded into the SPM at loading time, and the contents of the SPM does not change during runtime. The instructions that are not loaded into the SPM must be fetched directly from the main memory. In dynamic management, on the other hand, the mapping is one to many such that an SPM address can be mapped to many different main memory addresses. When the code of a program is managed in a dynamic way, the contents of the SPM are updated as the program executes by executing DMA loading operations at runtime. Many small applications can benefit

from static management as there is no runtime overhead, but for large applications, the overhead of accessing the slow main memory can outweigh. Dynamic management is inherently more advanced as it can exploit the locality of large applications. All management techniques proposed in this thesis perform dynamic management.

#### 1.2 Overview of This Thesis

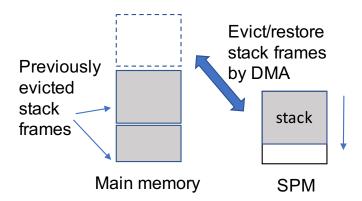

This thesis presents dynamic SPM management techniques that optimize the WCET of a given program, particularly focusing on managing program code and stack data. For managing program code, our work is based on function-level overlaying mechanism (Pabalkar et al., 2008; Baker et al., 2010) where a whole function is loaded to the SPM before it is called. Functions are loaded and evicted according a mapping of functions to SPM addresses, which are decided at compile-time. As loading a function using a direct memory access (DMA) transfer is a long-latency operation, it is critical to intelligently allocate SPM space to functions. In Chapter 2, we describe an optimal SPM space allocation technique to minimize the WCET. We further describe a heuristic to split functions into smaller partitions and discuss the impact of management granularities on the WCETs in Chapter 3. Our work for managing stack data is based on the dynamic management mechanism by Lu et al. (2013). In this mechanism, while the program stack is kept in the SPM, stack frames are evicted to and restored from the main memory at a call site to prevent the stack from growing larger than the SPM size. Since the size (depth) of the stack and the frequency of management operations for transferring stack frames would be different at different call sites, it is important to decide when to perform such operations. This problem can be seen as scheduling of stack management operations, and we describe an optimal technique for finding call sites to perform the management operations in Chapter 4.

#### 1.3 Contributions

The ultimate goal of this work is to enable correct-by-construction timing of hard real-time systems, which can guarantee the correct timing behavior at design-time or compile-time, without exhaustive testing. As stated earlier in this chapter, the pessimistic static analysis for existing cache-based architectures was a stumble stone in this regard. The significant reduction in the WCET estimates by the proposed techniques, compared to caches, can be seen that this is a step forward toward the goal of correct-by-construction timing of hard real-time systems. Other main contributions of this thesis are as follows.

- Finding optimal solutions in dynamic management: All techniques presented in this thesis perform dynamic management and can find optimal solution to minimize the WCET of a given program. All previously published techniques, regardless for allocating program code or for scheduling stack management operations, can only find optimal solutions for static management (Falk and Kleinsorge, 2009; Suhendra et al., 2005) or are optimized for the average-case performance (Avissar et al., 2002). Though claimed to be optimal for the worst-case, some work solves a very limited subset of a problem like selecting instructions in non-nested loops (Wu et al., 2010) or cannot really find an optimal solution as it takes one nominal input assumed to be the worst-case scenario (Whitham and Audsley, 2012; Liu and Zhang, 2015).

- Extensive evaluations: The effectiveness of the proposed managed techniques are thoroughly verified by extensive evaluations. We use not only several benchmarks from the Mälardalen WCET suite (Gustafsson *et al.*, 2010a) and MiBench suite (Guthaus *et al.*, 2001), but also three proprietary real-world applications from industry, for automotive powertrain control. In chapter 3, we compare against static analysis results for various previous techniques and caches, with several different architectural configurations.

#### 1.4 Related Publications

The main body of this thesis is composed of three chapters, each of which is a paper under review for publication.

Chapter 2 is an extended version of a published paper <sup>2</sup>. It is under review as of January 2017 at journal, ACM Transactions on Embedded Computing Systems (TECS), with a title of "WCET-Aware Function-level Dynamic Code Management on Scratchpad Memory". I invented all technical parts of this work, including input representation, analysis techniques, integer linear programming formulation, and the heuristic algorithm. All evaluations are also designed and performed by myself. The contributions of co-authors include, but not limited to, the formalism in writing of input representation and algorithm descriptions (David Broman) and the implementation of software infrastructure for constructing control-flow graphs and an early version of cache analysis technique (Jian Cai).

Chapter 3 is under review as of January 2017 at ACM Transactions on Architecture and Code Optimization (TACO), with a tile of "A Comparison of WCET-Centric Dynamic Code Management Techniques for Scratchpads". I am the sole contributor of this work.

Chapter 4 is under review as of January 2017 for publication in the proceedings of the 54th IEEE/ACM Design Automation Conference (DAC). I am the sole technical contributor in this work as well. I developed and implemented all algorithms. I also designed and performed all evaluations. A co-author, Jian Cai, helped with implementing a previous work for comparison, with extensive discussions.

<sup>&</sup>lt;sup>2</sup> ©2014 IEEE Yooseong Kim, David Broman, Jian Cai, and Aviral Shrivastava, "WCET-aware dynamic code management on scratchpads for Software-Managed Multicores", In Proceedings of Real-Time and Embedded Technology and Applications Symposium (RTAS), Apr., 2014. The publisher (IEEE) does not require individuals working on a thesis to obtain a formal reuse license.

# Chapter 2

#### WCET-AWARE FUNCTION-LEVEL DYNAMIC CODE MANAGEMENT<sup>1</sup>

SPM has time-predictable characteristics since its data movement between the SPM and the main memory is entirely managed by software. One way of such management is dynamic management. In dynamic management of instruction SPMs, code blocks are dynamically copied from the main memory to the SPM at runtime by executing direct memory access (DMA) instructions. Code management techniques try to minimize the overhead of DMA operations by finding an allocation scheme that leads to efficient utilization. In this chapter, we present three function-level code management techniques. These techniques perform allocation at the granularity of functions, with the objective of minimizing the impact of DMA overhead to the worst-case execution time (WCET) of a given program.

### 2.1 Introduction

In this chapter, we describe techniques that allocate code blocks to SPM, called code management techniques, and the objective of the techniques is to reduce the WCET of a given program. Compared to previous code management techniques that try to reduce WCET (Falk and Kleinsorge, 2009; Prakash and Patel, 2012; Puaut and Pais, 2007; Wu *et al.*, 2010), our techniques have two distinct characteristics.

The first difference is at the granularity of management. Code management techniques perform management at various levels of granularity, such as basic blocks (Steinke *et al.*,

<sup>&</sup>lt;sup>1</sup> This chapter extends a published paper, ©2014 IEEE, Yooseong Kim, David Broman, Jian Cai, and Aviral Shrivastava, "WCET-aware dynamic code management on scratchpads for Software-Managed Multicores", In Proceedings of Real-Time and Embedded Technology and Applications Symposium (RTAS), Apr., 2014. The publisher (IEEE) does not require individuals working on a thesis to obtain a formal reuse license.

2002a; Janapsatya *et al.*, 2006; Puaut and Pais, 2007; Wu *et al.*, 2010), groups of basic blocks on a straight-line path (Verma *et al.*, 2004), or fixed-size pages (Egger *et al.*, 2006). In this chapter, we focus on function-level code management techniques (Baker *et al.*, 2010; Pabalkar *et al.*, 2008; Jung *et al.*, 2010; Bai *et al.*, 2013), which load code blocks at the granularity of functions.

The second difference also comes from the function-level management. In function-level management, a function is loaded as a whole, and instructions are always fetched from the SPM, not the main memory <sup>2</sup>. Other management schemes, on the other hand, allocate only part of the instructions to the SPM and leave the rest in the main memory. The accesses for the instructions left in the main memory are assumed to be uncached and slow or to be cached, which can be less time-predictable.

All previous function-level code management techniques aim to optimize average-case execution time (ACET), by reducing overall DMA operation overhead, but none of them considers WCET. We present the first and only function-level code management techniques that optimize the WCET of a given program. Also, all previous techniques use function-to-region mappings (Pabalkar et al., 2008) to allocate SPM space to functions. The proposed techniques cannot only find an optimal function-to-region mapping for WCET, but can also find an optimal region-free mapping that maps functions directly to SPM addresses, not regions, which can lead to a lower WCET than the optimal function-to-region mapping. We evaluate our approach using several benchmarks from Mälardalen suite (Gustafsson et al., 2010a), MiBench suite (Guthaus et al., 2001), and proprietary automotive control applications from industry. The evaluation results show that our techniques can effectively reduce the WCETs of programs.

<sup>&</sup>lt;sup>2</sup> This makes function-level code management techniques only viable options in software-managed multicore architectures (Bai *et al.*, 2013), like IBM Cell processor (Kahle *et al.*, 2005), in which cores cannot directly access the main memory.

# 2.2 Background: Function-level Dynamic Code Management

When the SPM is large enough to store all instructions, running a program is very simple; the whole program can be loaded at loading time before execution. Dynamic code management, however, becomes necessary once the code size becomes larger than the SPM size. In dynamic management, compiler inserts DMA instructions for loading operations so that the contents stored in the SPM can be updated with different instructions at runtime. Management techniques coordinate DMA operations in order to avoid the overhead of such DMA operations.

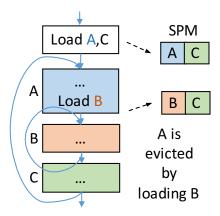

Function-level code management (Pabalkar *et al.*, 2008) loads instructions at the granularity of functions around each call site. Since it is assumed that the core fetches instructions only from the SPM, a whole function must be loaded in the SPM before executing the function. This imposes a limitation that the largest function in a program must fit in the SPM in order to be executable using function-level code management techniques. Where to load each function is decided at compile time, and in all previous approaches, such decisions are represented by function-to-region mappings. A function-to-region mapping is a surjective map from all functions in the program to all regions in the SPM.

Code management using function-to-region mappings is analogous to a direct-mapped cache. A region corresponds to a cache line. As memory addresses are mapped to cache lines, functions are mapped to regions. A function is always loaded to the starting address of its region, so loading a function always replaces any previously loaded function in the region. At a call (return), the compiler-inserted code looks up the state of the region to check if the callee (caller) function is loaded in the region. If not, the function is loaded by a DMA operation, and the core waits until it finishes before proceeding to execute the function. This process is analogous to tag comparison and cache miss handling in caches.

# (a) An example program

# (b) Mapping A

# (c) Mapping B

|   |   | Mapping size     | ACET                     | WCET            |

|---|---|------------------|--------------------------|-----------------|

| 1 | A | max(3,1) + 2 = 5 | 14 * 0.3 + 8 * 0.7 = 9.8 | max(14,8) = 14  |

| ] | В | max(3,2) + 1 = 4 | 11 * 0.3 + 11 * 0.7 = 11 | max(11,11) = 11 |

# (d) ACET and WCET comparison

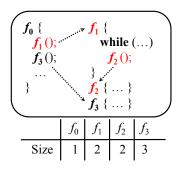

**Figure 2.1:** Mapping A optimizes the more frequently executed path (Path 2), achieving a better ACET than mapping B. In terms of WCET, however, mapping B is a better solution.

## 2.3 Motivating Examples

In this section, we use a simple motivating example to demonstrate the difference between the mapping optimized for ACET and the mapping optimized for WCET. Then, we show another motivating example to explain the benefit of mapping functions directly to address, instead of regions.

## 2.3.1 Why Do We Need a New Technique for Optimizing WCET?

Figure 2.1(a) shows an example program with three functions:  $f_0$ ,  $f_1$ , and  $f_2$ . The main function  $f_0$  has two paths, calling functions  $f_1$  on Path 1 and  $f_2$  on Path 2. The probability of the program to take each path is determined by the branch probability of the if-statement in  $f_0$ . The execution time of each path excluding the waiting time for DMA operations and path probabilities are also shown in the figure. The cost for loading each function is assumed to be the same as the size of the function.

Let us assume the size of the SPM is 5. Since the sum of all function sizes is larger than the SPM size, not all functions can have a private region. Here, we consider two feasible mapping solutions: mapping  $f_0$  and  $f_1$  to the same region (Mapping A) and mapping  $f_0$  and  $f_2$  to the same region (Mapping B). Figure 2.1(b) and 2.1(c) compare the sequence of DMA operations on each path for each mapping choice. For instance, with mapping A,  $f_0$  must be loaded again when  $f_1$  returns because  $f_0$  was evicted by  $f_1$ .

Figure 2.1(d) shows the ACET and the WCET for each mapping. Considering path probabilities, mapping A achieves a better ACET than mapping B. The overall amount of DMA transfers is less with mapping A because it can avoid evicting the largest function,  $f_0$ , on the more frequently executed path, Path 2. The WCET of the program is, however, better with mapping B  $^3$ .

All previous approaches use *interference cost* to model the cost of mapping two functions into the same region. For example, Bai *et al.* (2013) calculates the calories cost of mapping two functions A and B into one region as  $p_A \times p_B \times min(n_A, n_B) \times (s_A + s_B)$ , where  $p_f$ ,  $n_f$ , and  $s_f$  denote the execution probability, the iteration count, and the size of function f. Thus, the interference cost of mapping  $f_0$  and  $f_1$  into one region is  $1 \times 0.3 \times min(1,1) \times (3+1) = 1.2$ . Similarly, the cost of mapping  $f_0$  and  $f_2$  into the same region

<sup>&</sup>lt;sup>3</sup> In fact, the best mapping for both the ACET and the WCET would be mapping  $f_1$  and  $f_2$  into the same region and leaving  $f_0$  in a private region, but we only consider mapping A and B for illustrative purposes.

is  $1 \times 0.7 \times min(1,1) \times (3+2) = 3.5$ . Trying to minimize the interference cost, the technique from Bai *et al.* would always try to map  $f_0$  and  $f_2$  to different regions, and any other previous approaches would work similarly.

This example shows that optimizing for the ACET may not always result in a good WCET. Previous mapping techniques only try to optimize the ACET and are therefore not suitable for systems with strict timing constraints.

# 2.3.2 Why Do We Need Region-Free Mapping?

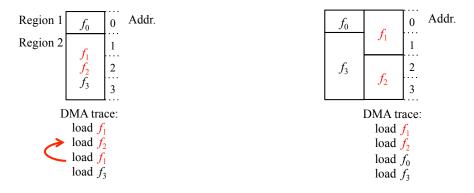

Figure 2.2(a) shows an example program with four functions,  $f_0$ ,  $f_1$ ,  $f_2$ , and  $f_4$ .  $f_0$  first calls  $f_1$ , and then  $f_1$  calls  $f_2$  in a loop. After  $f_1$  returns,  $f_0$  calls  $f_3$ . The execution sequence of the functions is  $f_0f_1(f_2f_1)^nf_0f_3f_0$ , where n is the number of iterations of the loop in which  $f_2$  is called. We assume  $f_0$  is preloaded before execution.

Let us assume the SPM size is 4. When a function-to-region mapping is used, it is not possible to assign separate regions to  $f_1$  and  $f_2$ . This is because the size of the largest function,  $f_3$ , is 3, so at least one region has to be as large as 3. The remaining SPM space is only 1, and the only function that can fit in a region whose size is 1 is  $f_0$ . Thus, the optimal function-to-region mapping, shown in Figure 2.2(b), is to map  $f_0$  in one region of size 1, and all the rest to the other region of size 3. With this mapping,  $f_0$  is kept loaded in a separate region, so it is not reloaded again when other functions return. This mapping, however, causes  $f_1$  and  $f_2$  to replace each other repetitively in the loop, causing DMA operations in every iteration. This is a significant overhead and can greatly increase the WCET of the program.

If we can map each function directly to an address range, not a region, this problem can be solved. As shown in Figure 2.2(c),  $f_1$  and  $f_2$  can be mapped to disjoint address ranges, from 0 to 1 and from 2 to 3, respectively. This can greatly improve the WCET because B and C can stay loaded after their initial loadings. This mapping causes  $f_1$  to be reloaded

### (a) An example program

(b) Optimal function-to-region mapping

(c) Optimal region-free mapping

**Figure 2.2:** Even with the optimal function-to-region mapping,  $f_1$  and  $f_2$  replace each other repetitively in the loop. Region-free mapping load them to disjoint address ranges, keeping them loaded after initial loadings.

when  $f_1$  returns back to  $f_0$  because their allocated SPM spaces overlap, but it happens only once. When  $f_3$  returns,  $f_0$  does not need to be reloaded.

# 2.4 WCET Analysis

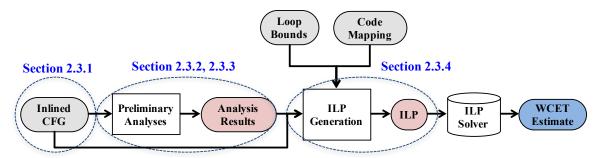

In order to find a mapping that can optimize the WCET of a program, we first need to be able to estimate the WCET of the program for a mapping—which can be either a function-to-region mapping or a region-free mapping. Figure 2.3 shows an overview of our WCET analysis framework. Given a graph representation of the program, we need to perform two analyses to obtain necessary information about the program. Using this information, along

Figure 2.3: The flow of our WCET analysis for function-level dynamic code management

with a mapping, and loop bounds, we formulate an integer linear programming (ILP) to compute a safe upper bound of the WCET.

### 2.4.1 Inlined Control Flow Graph

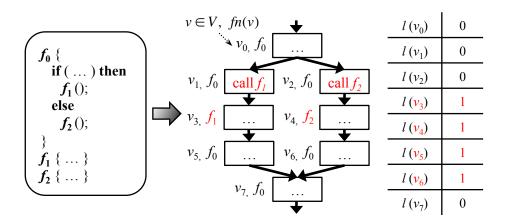

We use a variant of control flow graph (CFGs), called *inlined* CFGs, to represent a given program. An inlined CFG is a CFG of a whole program, not just one function, whose edges represent not only control flows within a function but also function calls and returns. An example program is depicted in Figure 2.4. In this example, like the example from Figure 2.1(a), the main function,  $f_0$  has one branch and calls  $f_1$  and  $f_2$ . We assume that both  $f_1$  and  $f_2$  consist of a single basic block. When  $f_0$  calls  $f_1$  at  $v_1$ , the CFG of  $f_1$  is inlined as  $v_3$ , and similarly the CFG of  $f_2$  is inlined as  $v_4$ . The notable benefit with this representation is that context information or call stack trace is explicit at any node in a graph, which avoids pessimism regarding uncertainties with call history in static analysis. One limitation is that recursive functions cannot be represented, which can be acceptable in the context of real-time embedded applications. Note that this is only a program representation for analysis. Any program can be represented in an lined CFG without actual inlining or any other modification.

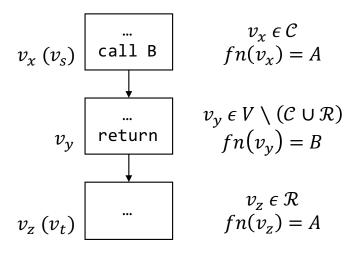

Let  $G = (V, E, v_s, v_t, F, fn)$  be an inlined CFG. V is the set of vertices, each of which is a basic block. The set of edges is defined as  $E = \{(v, w) | \text{ there is a direct path from } v \text{ to } w \text{ due to control flow, a function call or a return, where } v, w \in V.\}$ . Unlike basic blocks

**Figure 2.4:** Inlined CFG represents the global call sequence and the control flow by inlining the CFG of the callee function at each function call.

in conventional CFGs, function call instructions are always at the end of a basic block and cannot be in the middle of a basic block. Vertices  $v_s$  and  $v_t$  represent the starting basic block and the terminal basic block. F is the set of functions in the program, and  $f_n: V \rightarrow F$  is a mapping stating that  $f_n(v)$  is the function that v belongs to.

A mapping  $l: V \rightarrow \{0,1\}$  identifies *loading points* of functions. For a vertex v, l(v) is 1 only when there is an immediate predecessor u such that  $fn(u) \neq fn(v)$ , which means there is an incoming edge from another function. Figure 2.4 illustrates fn(v) and l(v).

We also define the concept of paths and related notations as follows. A path is a finite sequence of vertices  $p = p_1, p_2, \cdots, p_k$  such that  $\forall 1 \leq i \leq k, \ p_i \in V$  and  $\forall 1 \leq i < k, \ \exists (v_i, v_{i+1}) \in E$ . The *i*-th vertex on *p* is denoted by  $p_i$ , and the length of a path *p* is denoted by len(p). A vertex can appear multiple times on a path for the presence of loops. Given a vertex v, P(v) denotes the set of all paths that start from  $v_s$  and end with an immediate predecessor of v. Thus, v itself is not included in P(v). For a path p and a function f,  $last(p, f) \in V \cup \{\bot\}$  denotes the last occurrence of f on p. Thus, if we let  $last(p, f) = p_i$ , then  $fn(p_i) = f$  and  $fn(p_j) \neq f$ ,  $i < j \leq len(p)$ . When f does not appear on p,  $last(p, f) = \bot$ .

# 2.4.2 Finding Initial Loading Points

A function needs to be loaded at least once when it is called for the first time, which is analogous to cold misses in caches. For vertex v that is a loading point of fn(v), if there is any execution path from  $v_s$  to v on which fn(v) has never been executed, we call v an initial loading point of fn(v). We have to assume that a DMA operation must take place at least once for initial loading in such a case.

We define a binary mapping  $il: V \rightarrow \{0,1\}$  to identify initial loading points of functions. For a vertex  $v \in V$ , il(v) is 1 only when v is an initial loading point of fn(v), which is determined using traditional dominance analysis (Khedker *et al.*, 2009) as follows.

$$il(v) = \begin{cases} 0 & \exists d \in SDOM(v), \ fn(d) = fn(v) \\ 1 & \text{otherwise.} \end{cases}$$

(2.1)

where SDOM(v) denotes the set of strict dominators of v. If there is any strict dominator d whose fn(d) value is the same as fn(v), function fn(v) can be safely assumed to have been loaded before executing v. Otherwise, v is an initial loading point. In the example program in Figure 2.4,  $v_3$  is a potential loading point of  $f_1$ , and its strict dominators are  $v_0$  and  $v_1$ . Since both  $v_0$  and  $v_1$  belong to  $f_0$ , not  $f_1$ ,  $v_3$  is an initial loading point of  $f_1$ , thus  $il(v_3) = 1$ . Similarly,  $v_4$  is also an initial loading point of  $f_2$ .

## 2.4.3 Finding the Interference among Functions

At a loading point v that is not an initial loading point, fn(v) is guaranteed to have been loaded before control reaches v. To determine if fn(v) is still loaded at v, we make a conservative assumption as follows. If there exists a function  $g \neq fn(v)$  that satisfy the following two conditions, we assume that fn(v) has been evicted from the SPM:

1. g and fn(v) share SPM space (Their allocated SPM spaces overlap.).

2. There exists a path  $p \in P(v)$ , on which g is executed between last(p, fn(v)) and v.

Satisfying two conditions means, in other words, that fn(v) could have been evicted by g on a path from last(p, fn(v)) to v. The first condition cannot be checked because the SPM addresses of functions are not decided before code mapping stage (Section 2.5). The second condition, however, can be checked by analyzing the given CFG.

If the second condition satisfies, fn(v) and g have *interference* at loading point v. Our interference analysis <sup>4</sup> finds the set of all functions that potentially interfere with f at all loading points v, namely *interference set*, defined as below.

**Definition 1 (Interference Set)** Let  $G = (V, E, v_s, v_t, F, fn)$  be an inlined CFG. For a vertex  $v \in V$  and a function  $f \in F$ , the interference set  $IS[v, f] \subseteq F \setminus \{f\}$  is the set of all functions that appear between the path between last(p, f) and v, excluding last(p, f) and v, for all paths  $p \in P(v)$ .

When last(p, f) is  $\bot$  for all path  $p \in P(v)$ ,  $IS[v, f] = \emptyset$ . The following equation restates the above definition.

$$\forall v \in V, f \in F, \quad IS[v, f] = \bigcup_{\forall p \in P(v)} \{fn(p_j) \mid i < j \le len(p), \ p_i = last(p, f)\}$$

(2.2)

Table 2.1 shows interference sets for the example in Figure 2.4. To help follow how interference sets are calculated at each vertex v, the table also shows the set of last(p, f) for all paths  $p \in P(v)$  on the right three columns.

In other words, interference set IS[v, f] is the set of functions that *could* evict f from the SPM before f is executed at v. The eviction can actually occur if any function in

<sup>&</sup>lt;sup>4</sup> The term "interference analysis" has been used in the context of compiler optimization, such as in register allocation or in optimizing parallel programs. Our interference analysis is different from any of those, but similar in the sense that the results are used to predict any side-effect of compiler decision. For example, allocating a register to a variable may cause additional spills of other interfering variables, and mapping a function to an SPM address may cause additional DMA overhead for reloading other functions interfering with the function.

**Table 2.1:** Interference sets for the example program in Figure 2.4

|                  | IC[., £]                                           | IC[., £]                          | $IS[v, f_2]$ | $\bigcup_{\forall p \in P(v)} \{last(p, f)\}$ |                   |                   |

|------------------|----------------------------------------------------|-----------------------------------|--------------|-----------------------------------------------|-------------------|-------------------|

|                  | $IS[V, J_0]$                                       | $IS[v, f_0] \mid IS[v, f_1] \mid$ |              | $f = f_0$                                     | $f = f_1$         | $f = f_2$         |

| $v_0, v_1, v_2,$ | $v_0, v_1, v_2, \qquad \emptyset \qquad \emptyset$ |                                   | Ø            | Ø or has only immediate                       |                   |                   |

| $v_3, v_4$       | V                                                  | V                                 | V            | predecessor of v.                             |                   |                   |

| $v_5$            | $\{f_1\}$                                          | Ø                                 | 0            | {v <sub>1</sub> }                             | {v <sub>3</sub> } | Ø                 |

| $v_6$            | $\{f_2\}$                                          | Ø                                 | Ø            | {v <sub>2</sub> }                             | Ø                 | {v <sub>4</sub> } |

| $v_7$            | Ø                                                  | $\{f_{0}\}$                       | $\{f_0\}$    | $\{v_5, v_6\}$                                | {v <sub>3</sub> } | {v <sub>4</sub> } |

IS[v,f] is assigned an SPM space that overlaps with the SPM space assigned for f. Since a loading point v loads fn(v), only IS[v,fn(v)] is meaningful in estimating DMA costs. Nevertheless, the interference sets are calculated for all functions at each vertex to pass down the information to successor vertices.

We can safely assume that fn(v) is still loaded in the SPM only if: i) v is not an initial loading point of fn(v) ( $fn(v) \notin A[v]$ ), and ii) none of the functions in IS[v, fn(v)] shares SPM space with fn(v). Otherwise, we have to assume a DMA transfer will take place at v to load fn(v).

Interference sets can be calculated by a form of forward data-flow analysis, using the following data-flow equations. Algorithm 1 shows the procedure of using the equations. Let IN[v, f] and OUT[v, f] be the interference sets IS[v, f] before and after executing v,

## **Algorithm 1:** Interference analysis

**Input**: Inlined CFG (*G*)

**Output**: The interferense sets (*IS*)

1 **foreach**  $(v, f) \in V \times F$  **do**  $IN[v, f] \leftarrow \emptyset$

2 repeat

foreach

$$(v, f) \in V \times F$$

do

Evaluate Equations (2.3) and (2.4)

**until** IN[v, f] and OUT[v, f] stay unchanged for all  $v \in V$  and  $f \in F$

4 foreach

$$(v, f) \in V \times F$$

do

$| IS[v, f] = IN[v, f] - \{f\}$

respectively.

$$IN[v, f] = \bigcup_{(u,v) \in E} OUT[u, f]$$

(2.3)

$$IN[v, f] = \bigcup_{(u,v)\in E} OUT[u, f]$$

$$OUT[v, f] = \begin{cases} \emptyset & \text{if } f \neq fn(v) \land IN[v, f] = \emptyset \\ \{fn(v)\} & \text{if } f = fn(v) \end{cases}$$

$$IN[v, f] \cup \{fn(v)\} & \text{otherwise.}$$

$$(2.3)$$

Input value, IN[v, f], is the union of output values from all predecessors, and there are three different cases regarding how output value, OUT[v, f], is updated. First, when f is not fn(v), OUT[v, f] remains empty unless IN[v, f] has any function in it. IN[v, f] can become a non-empty set only when f has been executed previously, which is done by the second condition. The second condition says that when f is fn(v), any collected execution history in IN[v, f] is reset and the output value contains only fn(v). Once this happens, starting from the successors u of v, IN[u, f] will not be an empty set, and the function execution history can be recorded by taking a union of the input value and fn(u), as seen in the third condition. Notice that Algorithm 1 sets IS[v, f] to be  $IN[v, f] - \{f\}$  at line 4, after all the data-flow values converge, to make the final results comply to the definition that IS[v, f] does not contain f.

## 2.4.4 ILP Formulation for WCET Analysis

We describe an integer linear programming (ILP) formulation to find a safe upper bound of the WCET of a given program, when a particular function-to-region mapping for the program is given as input. Variables in the following ILP are written in capital letters, and constants are in small letters. The formulation requires that the input inlined CFG G to be acyclic, so we require G to be reducible and remove all back edges first.

The high-level structure of our formulation is similar to the one from the previous work (Suhendra *et al.*, 2005; Falk and Kleinsorge, 2009) in two aspects: i) a WCET estimate is obtained by accumulating the cost of each basic block backward from the end to the start of the program (Equation (4.2)), and ii) the objective is to minimize the WCET (Equation (4.1)). There are, however, significant differences in the rest of the formulation as we model the function loading cost at each vertex (Equation (2.13)).

Let  $W_v$  be a WCET estimate from v to the end of the program. Thus,  $W_{v_s}$  is a WCET estimate for the whole program. The objective is to get a safe-yet-tight estimate of the WCET of the program as follows.

$$minimize \quad W_{v_c}$$

(2.5)

Each vertex v can contribute to the WCET with the sum of its computation cost  $C_v$  and its loading cost  $L_v$ .  $C_v$  is the time to execute all instructions in v, which excludes the time to execute DMA instructions, which is  $L_v$ . For each successor w of v,  $W_v$  is greater than or equal to the sum of the cost of v and the cost of w. This makes  $W_v$  be a safe upper bound of the WCET from v to the end of the program. The terminal basic block does not have any

successor, so  $W_{v_t}$  is the cost of itself.

$$\forall (v, w) \in E, \quad W_v \ge W_w + C_v + L_v$$

$$W_{v_t} = C_{v_t} + L_{v_t}$$

(2.6)

The computation cost  $C_v$  is a product of the number of times v is executed in the worst-case  $(n_v)$  and the worst-case estimation of the time it takes to execute the instructions in v for once  $(c_v)$ .

$$C_{v} = n_{v} \cdot c_{v} \tag{2.7}$$

For loading cost  $L_v$  to exist, v must be a loading point, i.e., l(v) = 1. To employ the value of l(v) in the formulation, l(v) is imported as a constant  $l_v$  as below. Similarly, the information regarding initial loading point, il(v), is imported as a constant  $il_v$ .

$$l_{v} = l(v) \tag{2.8}$$

$$il_{v} = il(v) \tag{2.9}$$

The mapping information is taken into account as follows. For a pair of functions, f and g, a binary constant  $o_{f,g}$  is only one when their allocated SPM address ranges overlap. When the mapping is function-to-region mapping, this means that both functions are mapped to the same region. With a region-free mapping, this is calculated using the mapped address and the size of each function.

$$o_{f,g} = \begin{cases} 1 & \text{if the allocated SPM spaces for } f \text{ and } g \text{ overlap} \\ o & \text{otherwise.} \end{cases}$$

(2.10)

Let  $d_f$  denotes the time it takes to load function f by a DMA operation plus the overhead of executing DMA instructions. The loading cost  $L_v$  is modeled as follows. Table 2.2 shows different scenarios in which loading cost  $L_v$  can exist. If there exists any interfering

**Table 2.2:** Categorization of function loading cost at vertex v

|                                                        | Initial loading point          | Non-initial loading |  |

|--------------------------------------------------------|--------------------------------|---------------------|--|

|                                                        | $(il_v = 1)$                   | point $(il_v = 0)$  |  |

| fn(v) shares SPM space with an                         |                                |                     |  |

| interfering function f                                 | Always-Miss (load $n_v$ times) |                     |  |

| $\exists f \in IS[v, fn(v)], o_{fn(v), f} = 1$         |                                |                     |  |

| No space sharing                                       | First-Miss                     |                     |  |

| $   (\forall f \in IS[v, fn(v)], o_{fn(v), f} = 0)   $ | (load only once)               | No loading          |  |

function whose allocated SPM space overlaps with that of fn(v), fn(v) needs to be reloaded every time v is executed.  $AM_v$  (Always-Miss) models the loading cost in this case.

$$\forall f \in IS[v, fn(v)], \quad AM_v \ge n_v \cdot d_{fn(v)} \cdot o_{fn(v), f} \tag{2.11}$$

Consider an initial loading point v that is executed more than once in a loop. If there is no interfering function or none of the interfering function shares SPM space with fn(v), fn(v) needs to be loaded only once.  $FM_v$  (First-Miss) models the loading cost in this case. The value of  $FM_v$  is  $d_{fn(v)}$  as fn(v) is loaded only once. If, however, any interfering function shares SPM space with fn(v), it becomes Always-Miss, and the value of  $FM_v$  should be the same as  $AM_v$ . The difference in  $AM_v$  and  $d_{fn(v)}$  is compensated by adding  $(n_v - 1) \cdot d_{fn(v)}$  to  $d_{fn(v)}$  as follows.

$$\forall f \in IS[v, fn(v)], \quad FM_v \ge d_{fn(v)} + (n_v - 1) \cdot d_{fn(v)} \cdot o_{fn(v), f}$$

(2.12)

Finally, since the loading cost is present only when  $l_v$  is 1, and its value is either  $FM_v$  or  $AM_v$ , it is modeled by the following constraint.

$$L_{v} = l_{v} \cdot (il_{v} \cdot FM_{v} + (1 - il_{v}) \cdot AM_{v})$$

(2.13)

After solving the above ILP, the objective value  $W_{v_s}$  is a safe WCET estimate of the given program running on an SPM-based architecture with dynamic code management using the given code mapping.

## 2.5 WCET Optimization

In this section, we present three techniques of finding a code mapping for optimizing the WCET. The first one is optimal and based on ILP, and the second one is a polynomial-time heuristic, but sub-optimal. These two techniques find a function-to-region mapping, whereas the third technique finds an optimal region-free mapping using ILP.

## 2.5.1 ILP Formulation for Optimal Function-to-region Mapping

We extend the ILP formulation in Section 2.4.4 to *explore all mapping solutions* instead of taking a fixed mapping solution as input. A function-to-region mapping solution is represented by the following binary variables.

$$\forall f \in F, r \in R, \quad M_{f,r} = \begin{cases} 1 & \text{if } f \text{ is mapped to } r \\ 0 & \text{Otherwise} \end{cases}$$

(2.14)

The number of regions used in a mapping solution can vary for different solutions. For example, all functions can be mapped to one region (there is only one region.), or each function can be mapped to a unique region (the number of regions is the same as the number of functions.). To handle various number of regions, we let the set of all regions, R, be a set of integers ranging from 1 to |F|, each of which represents a unique region. If a mapping solution uses only n < |F| regions, there will be (|F| - n) regions that do not have any functions mapped to them.

The following constraints ensure the feasibility of mapping solutions that the solver will explore. Firstly, every function is mapped to exactly one region.

$$\forall f \in F, \qquad \sum_{r \in R} M_{f,r} = 1 \tag{2.15}$$

Secondly, the sum of the region sizes is not greater than the SPM size.

$$\forall f \in F, r \in R, \quad S_r \ge M_{f,r} \cdot s_f$$

$$SPMSIZE \ge \sum_{r \in R} S_r \tag{2.16}$$

where SPMSIZE is the size of the SPM, and  $s_f$  is the size of function f.  $S_r$  is a variable that represents the size of the largest function mapped to r.

For a pair of functions f and g, and a region r, we use a binary variable  $M_{f,g,r}$  that is 1 only when f and g are both mapped to r. This is represented by the following logical condition between variables. If both f and g are mapped to r, only the constraints in Set 1 should satisfy but not the constraints in Set 2, and vice versa.

The above logical constraints can be integer-programmed using the standard way of formulating logical constraints (Bradley *et al.*, 1977) as follows.

$$\forall f, g \in F, r \in R, \quad M_{f,r} + M_{g,r} + B \cdot (1 - M_{f,g,r}) > 1$$

(2.17)

$$M_{f,r} + M_{g,r} \le 1 + B \cdot M_{f,g,r}$$

(2.18)

where B is a constant chosen to be large enough so that regardless of the value of  $M_{f,g,r}$ , both constraints should satisfy at the same time. In this case, B should be at least 2 to make  $M_{f,r} + M_{g,r} + B \cdot (1 - M_{f,g,r}) > 1$  satisfiable when  $M_{f,g,r}$  is 0.

Then, the constraints for  $FM_v$  and  $AM_v$  from the constraints in Equation (2.11) and Equation (2.12) need to be rewritten using  $M_{fn(v), f, r}$  as follows.

$$\forall f \in IS[v, fn(v)], r \in R, \quad AM_v \ge n_v \cdot d_{fn(v)} \cdot M_{fn(v), f, r}$$

(2.19)

$$FM_{\nu} \ge d_{fn(\nu)} + (n_{\nu} - 1) \cdot d_{fn(\nu)} \cdot M_{fn(\nu), f, r}$$

(2.20)

The solution of this ILP formulation is an optimal function-to-region mapping represented by the set of variables  $M_{f,r}$  for all function  $f \in F$  and region  $r \in R$ . The final objective value  $W_{v_s}$  is the WCET estimate for the found mapping solution.

## 2.5.2 WMP: A Heuristic Alternative to the ILP Formulation

The ILP-based technique from the previous section can find an optimal solution, but it can take a long time for an ILP solver to find one. As each function needs to be mapped to each region, and the number of regions can be as many as the number of functions, the solution space of the ILP grows exponentially with the number of functions. In our experiments with benchmarks in Section 2.6, it takes less than a second for a solver to find an optimal solution for 'cnt' which has 6 functions, but for '1REG' which has 28 functions, the solver cannot find an optimal solution in 3 hours.

To solve this problem, we present *WCET-aware Merging and Partitioning* (WMP), a polynomial-time heuristic technique which builds upon the ways of searching the solution space of our previous techniques, *function mapping by updating and merging* (FMUM) and *function mapping by updating and partitioning* (FMUP) (Jung *et al.*, 2010). As the name suggests, FMUM starts with assigning a separate region to every function and tries to merge regions so that the mapping can fit in the SPM and the cost of the mapping decreases, whereas FMUP starts with having only one region and iteratively partitions a region into two regions. While the cost function in these techniques estimates the overall amount of DMA transfers, we introduce a new cost function that estimates the WCET of the program.

Algorithm 2: WMP: a heuristic to find a function-to-region mapping for WCET

**Input**: Inlined CFG (*G*), SPM size (*S*) ( $S \ge \max_{f \in F} s_f$ )

**Output**: A feasible function-to-region mapping (M) (Size $(M) \leq S$ )

```

function WMP(G, S)

```

```

remove all back edges in G

1

T \leftarrow Topologically sorted vertices of G

2

M_m \leftarrow \text{Merge}(G, T, S)

3

M_p \leftarrow \text{Partition}(G, T, S)

4

if Cost(M_m,T) < Cost(M_p,T) then

5

M \leftarrow M_m

6

else

M \leftarrow M_p

7

8

return M

```

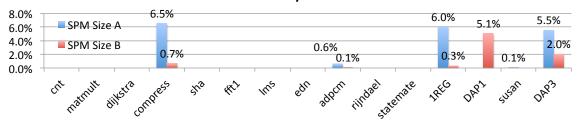

Before discussing the details of the WMP algorithm, we would like to point out that the ILP-based technique can also be used as a heuristic with a time limit set to the solver, as we do later in this chapter (Section 2.6). This makes the solver to output the best solution found by the time limit, which may not be optimal. In our experiments with 3-hour time limit, this ILP-based technique could always find solutions that are better (meaning that the resulting WCET is smaller) or at least as good as the solutions found by WMP. This, however, brings up another problem of choosing a time limit that is long enough to find good solutions. For example, in our experiments with benchmark '1REG', the ILP solver needed at least 50 seconds to find a solution as good as the solution found by WMP and at least 20 minutes to find a solution better than WMP's solution. On the other hand, WMP could find a solution within a second for all benchmarks, and the increase in WCETs compared to the ILP with 3-hour time limit is not greater than 6.5%. In this sense, WMP is still a reasonable and scalable alternative to the ILP.

**Algorithm 3:** Cost function that estimates the WCET for a given mapping M

**Input**: Function-to-region mapping (M), Topological-sorted vertex list (T)

```

Output: The WCET estimate (c[v_t])

```

```

function Cost(M,T)

initialize c[v] to 0 for all v \in V

1

for v in T from head to tail do

2

c \leftarrow n_v \cdot c_v

3

if l(v) = 1 then

4

if \exists f \in \mathit{IS}[v, \mathit{fn}(v)] such that \mathit{M}[\mathit{fn}(v)] = \mathit{M}[f] then

5

6

else

if il(v) = 1 then

7

8

9

return c[v_t]

10

```

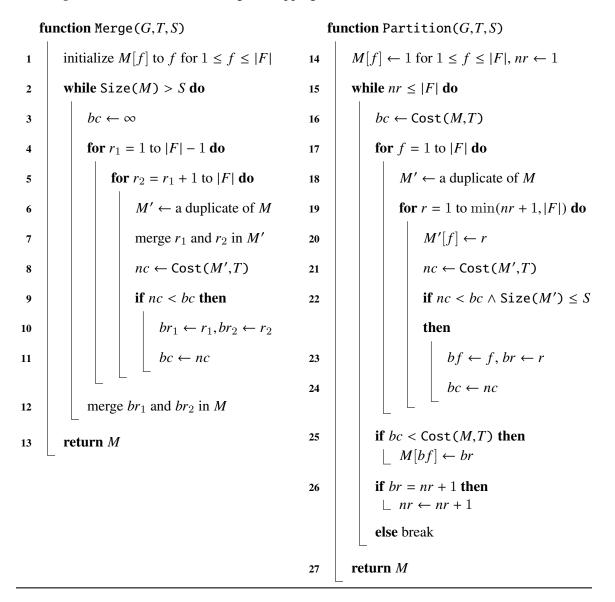

Algorithm 2 shows the pseudocode. Given an inlined CFG, the interference sets and the size of SPM, it returns a function-to-region mapping M. A mapping solution, M, is represented by an integer array whose size is the same as the number of functions. The ID of a function is represented by an array index, and its mapped region is the value of the array element. For example, if function 1 is mapped to region 2, M[1] = 2. It finds two mapping solutions by merging and partitioning (line 3-4), whose algorithms are shown in Algorithm 4. The one with a lesser cost is selected (line 5-7).

The cost of a mapping is the WCET estimate of it. We take the longest path in the input inlined CFG as an estimation of the WCET, and to find the longest path, we first remove all back edges from the graph and topologically sort the vertices at line 2-3 in Algorithm 2.

The cost function, Cost, shown in Algorithm 3 visits each vertex in topological order and calculates the computation cost (line 3) and the loading cost (line 4-8) for the given mapping. At each vertex v, the final cost of the vertex c[v] is the sum of its own cost and the maximum cost among the costs of all predecessors (line 9). Thus, the cost of the terminal vertex  $c[v_t]$  becomes the longest path length.

Algorithm 4 shows two heuristics, Merge and Partition. Merge starts with mapping each function to a separate region (line 1). In every iteration of the while loop at line 2-14, we take every pair of two regions (line 4-5) to merge and create a temporary mapping M' where two regions are merged (line 6-7). We check the cost of M' and keep a record of the best pair of regions to be merged and its cost (line 8-11). After trying all combinations, we change the original mapping M by merging the best pair of regions (line 12). The loop repeats until the mapping can fit in the SPM, i.e. the sum of the sizes of regions is smaller than SPMSIZE (line 2). Partition starts with mapping all functions to one region (line 14). Variable nr represents the current number of regions. Again, we create a duplicate of M and move each function f to a different region r, creating another region nr + 1 (line 18-20). We keep a record of the best combination of f and r, and its cost (line 21-24). After trying all functions, we move function bf to region br (line 25). The loop repeats until the number of regions is not greater than |F| (line 15) or until the number of regions stops increasing (line 26).

Function Size is defined in Algorithm 5. It calculates the memory size requirement of a given mapping *M* by summing up the size of the largest function in each region.

The while loop in Merge takes at most |F| - 1 times because the number of regions decreases by one at every iteration. The for-loop nest at line 5-7 takes  $|F|^2$  times at most. Merging two regions requires checking every array elements at least once to find all functions mapped to one region and move it to another region, which takes O(|F|) time complexity. The time complexity of Cost is  $O(|V| \cdot |F - 1|)$  since it visits every vertex only

Algorithm 4: Search feasible mapping solutions by merging and partitioning

**Input**: Inlined CFG (G), Topologically sorted vertex list (T), SPM size (S) ( $S \ge \max_{f \in F} s_f$ )

**Output**: A feasible function-to-region mapping (M) (Size $(M) \leq S$ )

once, and the number of functions in the interference set IS[v,fn(v)] can be at most |F|-1 because fn(v) is excluded in the set. Thus, the time complexity of function Merge is  $O(|F|^4 \cdot |V|)$ . Similarly, Partition has the same time complexity because the while loop and for loops at line 16, 18 and 20 iterate at most |F| times.

**Algorithm 5:** Find the SPM size requirement of a given function-to-region mapping

```

Input: Inlined CFG(G), function-to-regionfunction Size(M)Mapping (M), Function sizes1initialize S[r] to 0 for 1 \le r \le |F|(s_f, \forall f \in F)2for each f \in F doOutput: The SPM size that the given mapping M requires.3if S[M[f]] < s_f then S[M[f]] \leftarrow s_fM requires.4return \sum_{r \in R} S[r]

```

WMP algorithm always terminates. In Merge, the SPM size S is greater than or equal to the size of the largest function by assertion at the beginning, and the size of mapping, Size(M), is reduced after every iteration of while loop (line 2) by merging two regions (line 12). All for loops in Merge (line 4-5) have finite loop bound |F|, too. Function Cost finishes in a finite number of iterations because the vertex list has finite length |V| (line 10) and the interference sets can have at most |F|-1 vertices (line 13). Thus, Merge terminates in a finite number of steps. Similarly, Partition also finishes in a finite number of steps because at the end of every iteration, either the number of regions nr increases or the loop terminates (line 26).

WMP algorithm is sound and complete in that it always finds a solution which is a feasible mapping can fit in the SPM. Merge always returns a feasible mapping because in every iteration, two regions are merged in line 12 and the loop termination condition in line 2 ensures the feasibility of the mapping. The initial solution of Partition is mapping all functions into one region, which is certainly feasible because of the precondition:  $S \ge \max_{f \in F} s_f$ . During the execution of the algorithm, the mapping changes only in a way that the resulting mapping fits in the SPM (line 22).

WMP algorithm is, however, not optimal because it does not explore the entire solution space. As a heuristic, WMP trades optimality for speed. For example, Merge only con-

siders merging two regions at time in a greedy fashion. Once two regions are merged, the functions in the regions have to be mapped to the same region until the end of the algorithm.

## 2.5.3 Optimizing WCET using Region-free Mappings

Similarly to the Section 2.5.1, we extend the ILP for WCET analysis from Section 2.4.4 to explore all feasible region-free mapping solutions and find an optimal one.

Variable  $A_f$  represents region-free mapping of f, the address at which function f will be loaded, and it should be in the following range.

$$0 \le A_f \le \text{SPMSIZE} - s_f \tag{2.21}$$

where  $s_f$  denotes the size of function f. Then, the following constraints compare the mapped addresses of two functions and represent their relations. For a pair of functions f and g, binary variable  $G_{f,g}$  is 1 if  $A_f$  is greater than  $A_g$ , and 0 otherwise.

$$\forall f,g \in F \text{ such that } f \neq g, \qquad -\mathcal{M}(1-G_{f,g}) \leq A_f - A_g \leq \mathcal{M} \cdot G_{f,g}$$

$$G_{f,g} + G_{g,f} = 1$$

(2.22)

where  $\mathcal{M}$  is a sufficiently large integer, used to linearize the if conditions. In our formulation, SPMSIZE can be safely used as  $\mathcal{M}$ . For example, if  $G_{f,g}$  is 1, the above constraints become  $0 \le A_f - A_g \le \mathcal{M}$  and  $G_{g,f} = 0$ , so  $A_f$  have to be greater than or equal to  $A_g$ . If  $G_{f,g}$  is 0, the above constraints become  $-\mathcal{M} \le A_f - A_g \le 0$  and  $G_{g,f} = 1$ , so  $A_f$  have to be less than or equal to  $A_g$ .

The address range that is allocated to function f is  $[A_f + 0, A_f + 1, \dots, A_f + s_f - 1]$ , where  $s_f$  is the size of f. For a pair of functions f and g, to make sure that their addresses do not overlap, either one of the two constraints should be satisfied:  $A_f + s_f - 1 < A_g$  when  $A_f < A_g$  ( $G_{f,g} = 1$ ), or  $A_g + s_g - 1 < A_f$  when  $A_g > A_f$  ( $G_{g,f} = 1$ ). Built on this idea, the following constraints make binary variable  $O_{f,g}$  to be 1 if the address ranges of f and

g overlap, and 0 otherwise.

$$\forall f,g \in F \text{ such that } f \neq g, \quad A_f + s_f < A_g + 1 + \mathcal{M} \cdot G_{f,g} + \mathcal{M} \cdot O_{f,g}$$

$$\mathcal{M} \cdot (1 - O_{f,g}) + A_f + s_f \ge A_g + 1 + \mathcal{M} \cdot O_{f,g}$$

$$A_g + s_g < A_f + 1 + \mathcal{M} \cdot G_{g,f} + \mathcal{M} \cdot O_{f,g}$$

$$\mathcal{M} \cdot (1 - O_{f,g}) + A_g + s_g \ge A_f + 1 + \mathcal{M} \cdot O_{f,g}$$

$$O_{f,g} = O_{g,f}$$

$$(2.23)$$

For example, if  $A_f > A_g$  ( $G_{f,g} = 1$ ), the first four lines in the above become as follows.

$$A_f + s_f < A_g + 1 + \mathcal{M} + \mathcal{M} \cdot O_{f,g}$$

$$\mathcal{M} \cdot (1 - O_{f,g}) + A_f + s_f \ge A_g + 1 + \mathcal{M} \cdot O_{f,g}$$

$$A_g + s_g < A_f + 1 + \mathcal{M} \cdot O_{f,g}$$

$$\mathcal{M} \cdot (1 - O_{f,g}) + A_g + s_g \ge A_f + 1 + \mathcal{M} \cdot O_{f,g}$$

The first line becomes meaningless because of the third term,  $\mathcal{M}$ , on the right hand side, and the second line also becomes meaningless regardless of the value of  $O_{f,g}$  because  $A_f$  is greater than  $A_g$ . When the address ranges of f and g do overlap  $(A_g + s_g \ge A_f + 1)$ , the third line ensures that  $O_{f,g}$  becomes 1, and the fourth line becomes meaningless—it satisfies regardless of the value of  $O_{f,g}$ . When the address ranges do not overlap  $(A_g + s_g < A_f + 1)$ , the third line becomes meaningless, but the fourth line ensures that  $O_{f,g}$  becomes 0.

We rewrite the Equation (2.11) and Equation (2.12) with  $O_{f,g}$  variables as below.

$$\forall f \in IS[v, fn(v)], \quad AM_v \ge n_v \cdot d_{fn(v)} \cdot O_{fn(v), f}$$

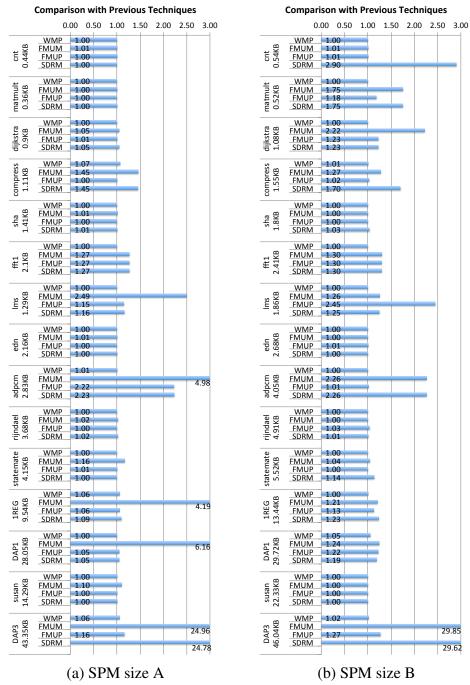

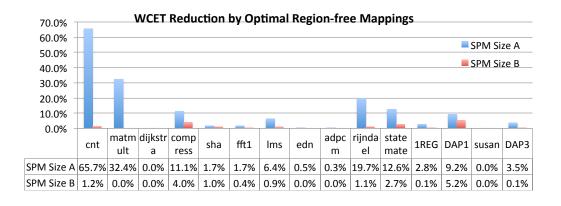

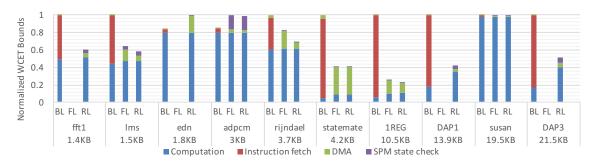

(2.24)