Scratchpad Management in Software Managed Manycore Architectures

by

Jian Cai

# A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved October 2017 by the Graduate Supervisory Committee:

Aviral Shrivastava, Chair Carole Wu Fengbo Ren Partha Dasgupta

ARIZONA STATE UNIVERSITY

December 2017

#### ABSTRACT

Caches have long been used to reduce memory access latency. However, the increased complexity of cache coherence can bring significant challenges in processor design as the number of cores increases. While making caches scalable is an important research problem, some researchers are also exploring the possibility of a more power-efficient SRAM called scratchpad memories or SPMs.

SPMs consume significantly less area, and are more energy-efficient per access than caches, and therefore makes the design of on-chip memories much simpler. Unlike caches, which fetch data from memories automatically and maintain coherence with other caches, an SPM requires explicit instructions to transfer code and data from and to main memory. SPM-only architectures are thus named as SMM architectures, since the data movements of such architectures rely on software. SMM processors have been widely used in different areas, such as embedded computing, network processing, or even high performance computing. SMM processors provide a low-power platform. However, the hardware alone does not guarantee the delivery of power efficiency, if applications on such processors suffer from low performance. Efficient software techniques are required. A big body of SPM management techniques for SMM architectures are compiler-directed, as inserting data movement operations by hand force programmers to trace flow of data, which can be error-prone and sometime very difficult. In this thesis, we develop compiler-directed techniques to efficiently manage different types of data of embedded applications between SPMs and main memory in SMM architectures, custom to unique characteristics of each type of data. Our approach takes as input a program, analyzes and finds out the proper program points, and inserts data movement instructions accordingly. Our approach manages code, stack and heap data, and reduce execution time by 14%, 52% and 80% respectively compared to their predecessors on typical embedded applications. Other than managing local data, we also develop management techniques to manage shared data in SMM architectures. Experimental results show our approach achieve more than 2X speedup than the previous technique on average.

#### Acknowledgement

PhD life is the most challenging yet the most rewarding time of my life. It not only teaches me how to think critically, but also makes me realize the importance of communicating clearly with people, a skill that keeps helping me even after graduate school. It lets me learn patience and persistence. I can never finish my 7 years of study without them. Most importantly, it allows me to find the passion of my life and start a career I love.

I would never complete my PhD study without the help I received. My advisor, Professor Aviral Shrivastava, enlightened me with his insight, and never lost faith in me. My labmates, Di Lu, Bryce Holton, Yooseong Kim, and Moslem Didehban, always encouraged me, and brainstormed with me when I faced technical difficulties. Mahesh Balasubramanian, Mohammadreza Mehrabian, Shail Dave, Mohammad Khayatian, and the rest labmates all offered their help so I could focus on the defense towards the end of my PhD life. My committee members, Professor Fengbo Ren, Professor Partha Dasgupta, and Professor Carole-Jean Wu, offered their valuable opinions so that I could refine my work. Because of all these lovely people, my PhD life was so enjoyable and memorable.

Finally, I would like to thank my parents and my girlfriend Tianran. There are so many times I felt lost in life, it was always their unconditional support that helped me through.

|      |      |            | Pa                                      | age  |

|------|------|------------|-----------------------------------------|------|

| LIST | OF 7 | TABLES     | S                                       | vii  |

| LIST | OF F | FIGURI     | ES                                      | viii |

| CHA  | PTER | ł          |                                         |      |

| 1    | INT  | TRODUCTION |                                         |      |

|      | 1.1  | Scrate     | hpad Memory                             | 1    |

|      | 1.2  | Softwa     | are Managed Manycore and Its Management | 4    |

|      | 1.3  | Overv      | iew of This Thesis                      | 7    |

|      |      | 1.3.1      | Efficient Code Management               | 7    |

|      |      | 1.3.2      | Efficient Stack Management              | 8    |

|      |      | 1.3.3      | Efficient Heap Management               | 8    |

|      |      | 1.3.4      | Shared Data Management                  | 9    |

| 2    | COI  | DE MA      | NAGEMENT ON SPM                         | 10   |

|      | 2.1  | Introd     | luction                                 | 10   |

|      | 2.2  | Relate     | ed Work                                 | 13   |

|      | 2.3  | Motiv      | ating Example                           | 15   |

|      | 2.4  | Our A      | pproach                                 | 16   |

|      |      | 2.4.1      | Notation                                | 17   |

|      |      | 2.4.2      | Always-hit Analysis                     | 18   |

|      |      | 2.4.3      | First-miss Analysis                     | 21   |

|      | 2.5  | Evalua     | ation                                   | 22   |

|      |      | 2.5.1      | Experimental setup                      | 22   |

|      |      | 2.5.2      | Code Management Overhead Reduction      | 23   |

|      |      | 2.5.3      | Comparison with Hardware Caching        | 24   |

|      | 2.6  | Conclu     | usion                                   | 26   |

# TABLE OF CONTENTS

# Page

| 3 | STA | CK MANAGEMENT ON SPM                            | 29 |  |

|---|-----|-------------------------------------------------|----|--|

|   | 3.1 | Introduction                                    | 29 |  |

|   | 3.2 | Related Work                                    | 31 |  |

|   | 3.3 | Background                                      |    |  |

|   | 3.4 | Key Ideas of Our Approach                       | 36 |  |

|   | 3.5 | Details of Our Approach                         | 38 |  |

|   |     | 3.5.1 Steps of Our Approach                     | 38 |  |

|   | 3.6 | Experiments                                     | 45 |  |

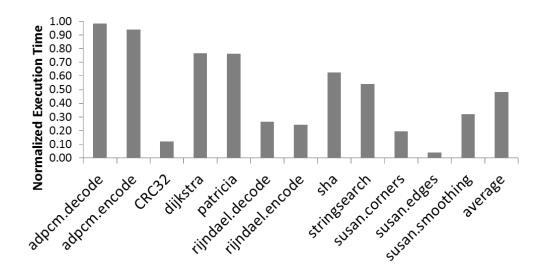

|   |     | 3.6.1 Improvement Over The State of The Art     | 45 |  |

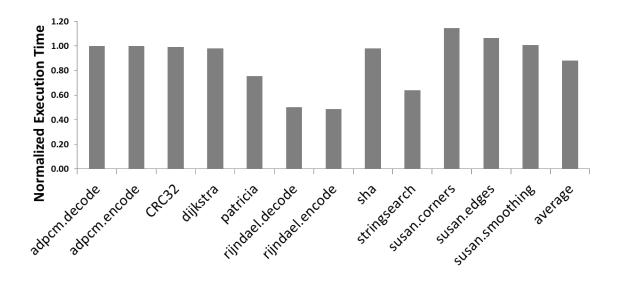

|   |     | 3.6.2 Comparable Performance Compared to Caches | 48 |  |

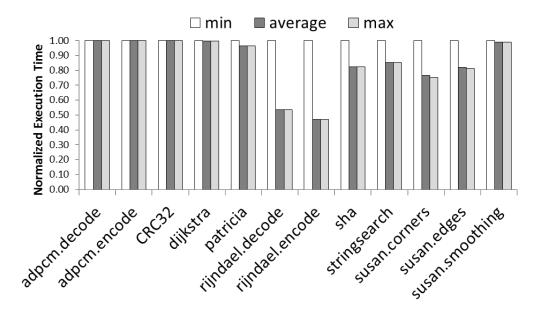

|   |     | 3.6.3 Choice of SPM Stack Size                  | 49 |  |

|   |     | 3.6.4 Integrated Management                     | 51 |  |

|   | 3.7 | Conclusion                                      | 52 |  |

| 4 | ОРЛ | TIMIZING HEAP DATA MANAGEMENT ON SOFTWARE MAN-  |    |  |

|   | AGE | ED MANYCORE ARCHITECTURES                       | 53 |  |

|   | 4.1 | Introduction                                    | 53 |  |

|   | 4.2 | Related Work                                    | 56 |  |

|   | 4.3 | Limitation of the State of The Art              | 58 |  |

|   | 4.4 | Key Ideas of Our Approach                       | 60 |  |

|   | 4.5 | Details of Our Approach                         | 61 |  |

|   |     | 4.5.1 Statically detect heap accesses           | 61 |  |

|   |     | 4.5.2 Simplify management framework             | 64 |  |

|   |     | 4.5.3 Inline and combine management calls       | 66 |  |

|   | 4.6 | Experiments                                     | 68 |  |

# Page

|      |      | 4.6.1  | Experimental setup                   | 68 |

|------|------|--------|--------------------------------------|----|

|      |      | 4.6.2  | Significantly reduces execution time | 70 |

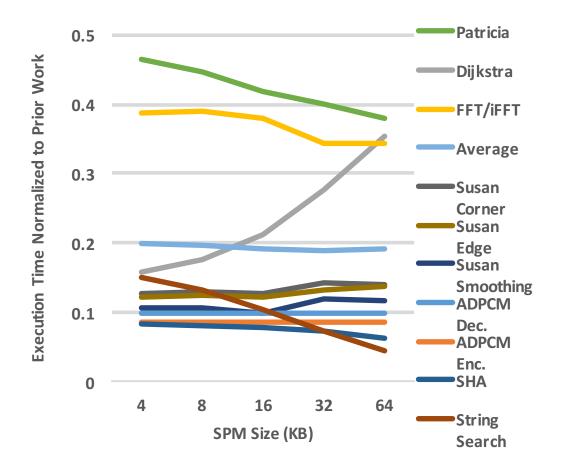

|      |      | 4.6.3  | Scales well with SPM size            | 73 |

|      | 4.7  | Conclu | ision                                | 75 |

| 5    | SHA  | RED I  | DATA MANAGEMENT                      | 78 |

|      | 5.1  | Introd | uction                               | 78 |

|      |      | 5.1.1  | Related Work                         | 80 |

|      |      | 5.1.2  | Previous Approach                    | 82 |

|      |      | 5.1.3  | Our Approach                         | 83 |

|      |      | 5.1.4  | Experimental Results                 | 87 |

| 6    | MY   | CONT   | RIBUTIONS                            | 93 |

| 7    | SUN  | IMARY  | r                                    | 94 |

| REFE | EREN | CES    |                                      | 96 |

# LIST OF TABLES

| Table | ]                                                                   | Page |

|-------|---------------------------------------------------------------------|------|

| 3.1   | Overhead Of Pointer Management                                      | . 45 |

| 4.1   | Maximum Heap Usage Of Benchmarks                                    | . 68 |

| 4.2   | Number Of G2l Calls Called Before And After Identifying Heap Access |      |

|       | Statically With The Previous Technique                              | . 70 |

| 4.3   | Instructions Executed Per G2l Under Different Cases With Optimiza-  |      |

|       | tions Incrementally Added.                                          | . 71 |

| 5.1   | Benchmarks                                                          | . 87 |

# LIST OF FIGURES

| Figure | I                                                                  | Page |

|--------|--------------------------------------------------------------------|------|

| 1.1    | Difference Between Cache And SPM—the Hardware View                 | 2    |

| 1.2    | Difference Between Cache And SPM—the Software View                 | 3    |

| 1.3    | An Example Of SMM Architectures.                                   | 4    |

| 1.4    | Our Approach Analyzes Programs And Inserts Management Instruc-     |      |

|        | tions For Efficient Data Movement Between SPM And Main Memory      | 7    |

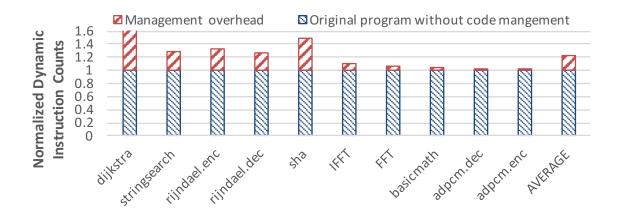

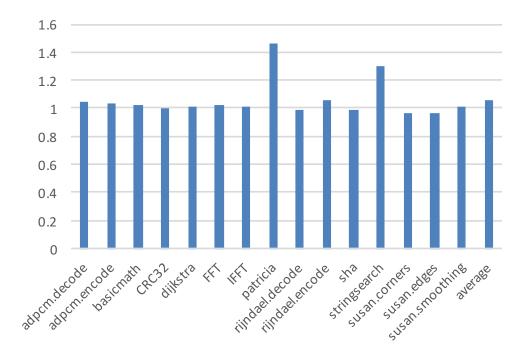

| 2.1    | Code Management Increases Instruction Count By $22\%$ On Average   |      |

|        | Even When The SPM Is Larger Than The Code Size                     | 11   |

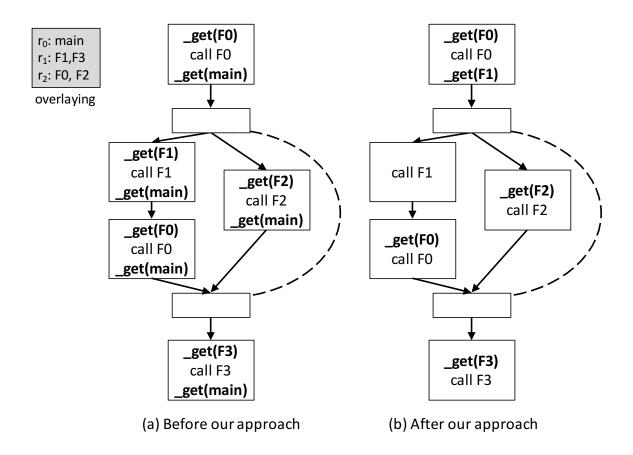

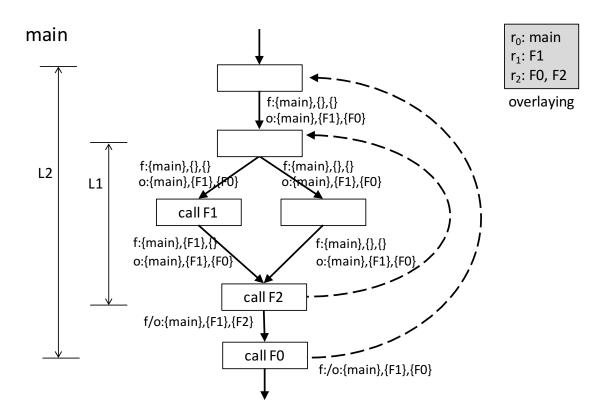

| 2.2    | Our Analysis Avoids Unnecessary Management Functions               | 15   |

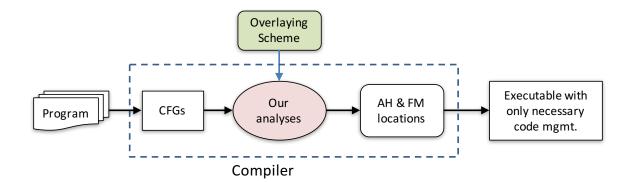

| 2.3    | Overview Of Our Approach.                                          | 16   |

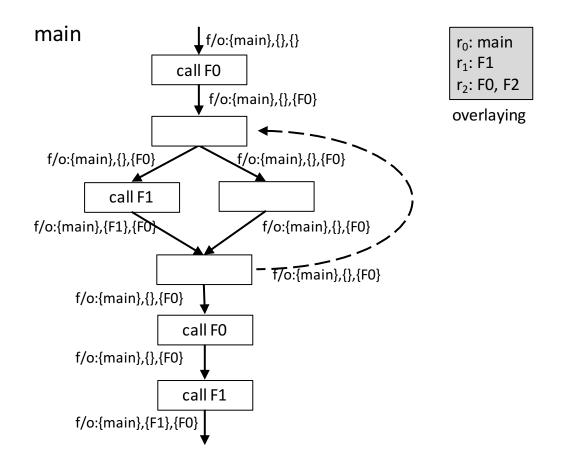

| 2.4    | Always-hit Program Points In Main Function, Given The Function-    |      |

|        | to-region Mapping                                                  | 19   |

| 2.5    | First-miss Program Points In Loop L2 Of Main Function              | 20   |

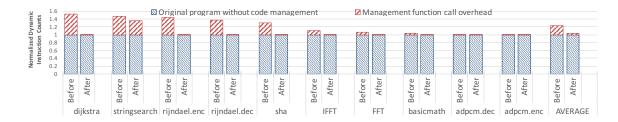

| 2.6    | Our Approach Reduces The Management Overhead By $84\%$ And The     |      |

|        | Overall Execution Time By 15% On Average                           | 23   |

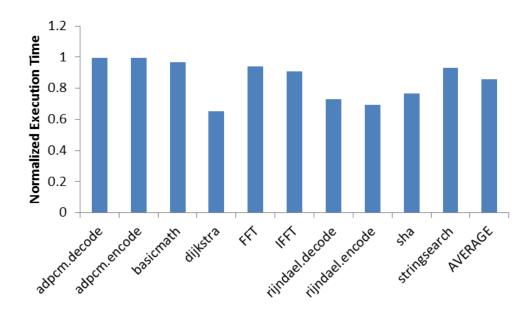

| 2.7    | Execution Time Is Reduced By Over 14% On Average                   | 24   |

| 2.8    | The Execution Times Are Normalized To Those With Hardware Caching. | 25   |

| 3.1    | Pointer Management Problem                                         | 30   |

| 3.2    | The Way Pointer Management Functions Work                          | 33   |

| 3.3    | The Key Ideas Of Our Approach.                                     | 36   |

| 3.4    | Identification Of The Potential Pointer To Stack.                  | 38   |

| 3.5    | The Analysis To Find Out At Which Stack Frames Will Exist In SPM   |      |

|        | At The Same Time                                                   | 40   |

| 3.6  | Compared To Previous Pointer Management, Our Approach Reuses      |    |

|------|-------------------------------------------------------------------|----|

|      | The Local Buffer Created By G2l Function And Saves Management     |    |

|      | Overhead.                                                         | 44 |

| 3.7  | The Compilation Process Of Benchmarks Used In Experiments         | 46 |

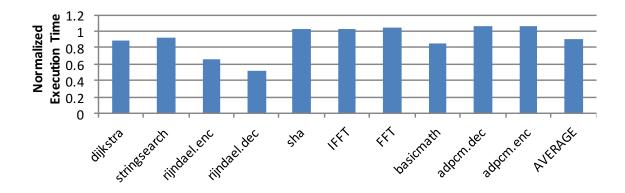

| 3.8  | Execution Time Of Our Approach Normalized To The Previous Pointer |    |

|      | Management.                                                       | 47 |

| 3.9  | Normalized Execution Time Of Our Approach Normalized To Caching.  | 49 |

| 3.10 | Execution Time Of Our Approach Using Three Different SPM Sizes,   |    |

|      | All Normalized To The Execution Time With The Minimum SPM Size.   | 50 |

| 3.11 | Execution Time Of Integrated Code And Stack Management, Normal-   |    |

|      | ized To The Execution Time Of Caching                             | 51 |

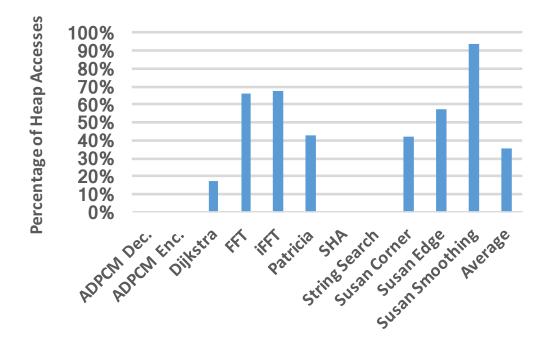

| 4.1  | Percent Of Heap Accesses Among All The Accesses (excluding Code   |    |

|      | Accesses).                                                        | 54 |

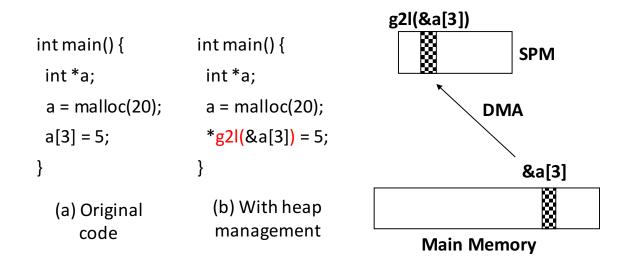

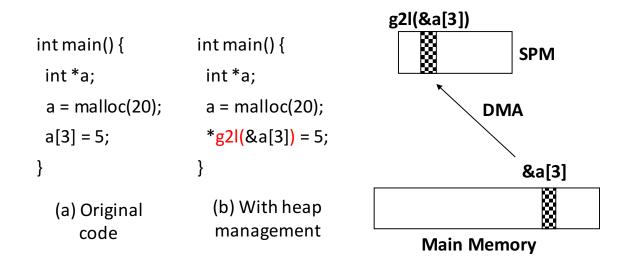

| 4.2  | How Heap Management Function G2l Works                            | 55 |

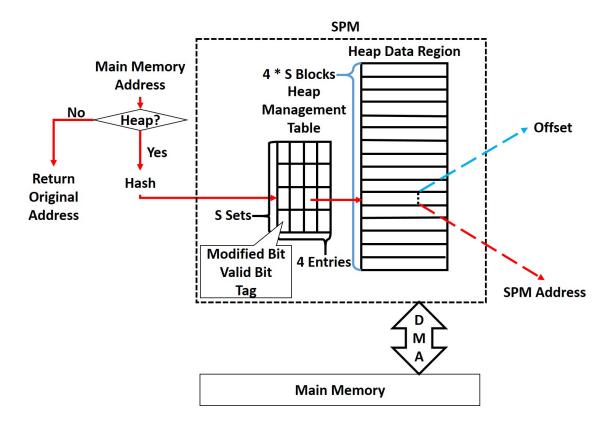

| 4.3  | The State-of-the-art Heap Management Approach                     | 57 |

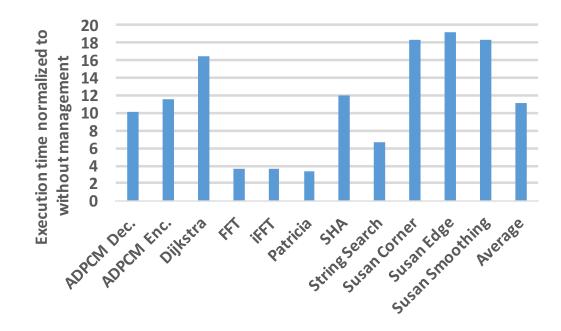

| 4.4  | Performance Overhead Caused By The State-of-the-art Heap Manage-  |    |

|      | ment Approach                                                     | 59 |

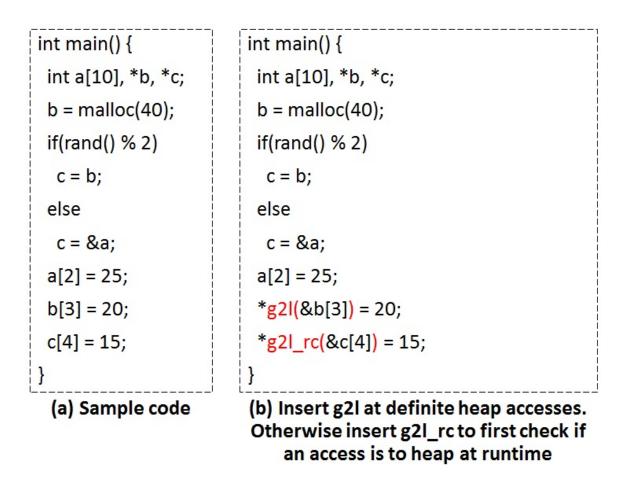

| 4.5  | The Previous Approach Inserts G2l Before Every Memory Access,     |    |

|      | While Our Approach Skips Unnecessary G2ls                         | 61 |

| 4.6  | When A Memory Access May Be To Heap But Is Not For Certain, We    |    |

|      | Check At Runtime Before Managing The Access                       | 63 |

| 4.7  | Reduced Complexity Of Our Approach Compared To The Previous       |    |

|      | Approach                                                          | 65 |

| 4.8  | We Inline Management Calls And Move Common Operations To The          |    |

|------|-----------------------------------------------------------------------|----|

|      | Beginning Of The Caller Function                                      | 66 |

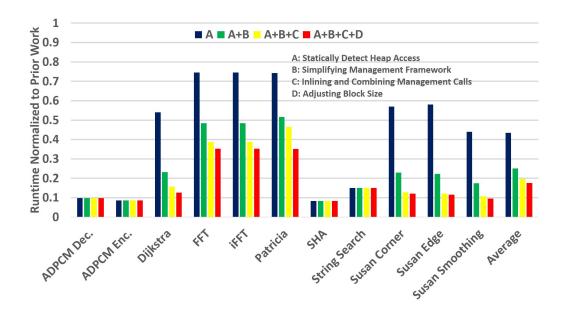

| 4.9  | The Execution Time Of Our Approach Normalized To The Previous         |    |

|      | Work With Optimizations Incrementally Added.                          | 69 |

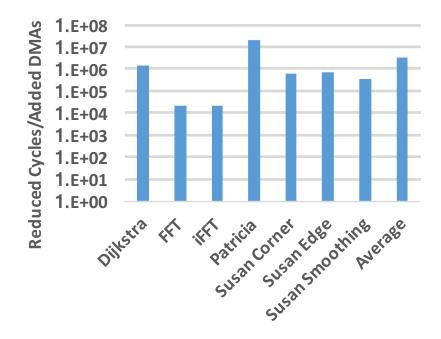

| 4.10 | Implementing A Direct-mapped Cache Other Than A 4-way Set-associative | Э  |

|      | Cache Reduces More Execution Time Than The Extra Time Intro-          |    |

|      | duced Due To Increased Cache Misses.                                  | 72 |

| 4.11 | Execution Time Of Our Approach Normalized To The Previous Work,       |    |

|      | When The SPM Size Increases From 4KB To 64KB                          | 74 |

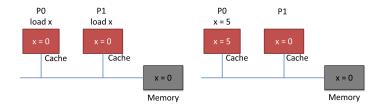

| 5.1  | An Example Of Cache Coherence Problem                                 | 79 |

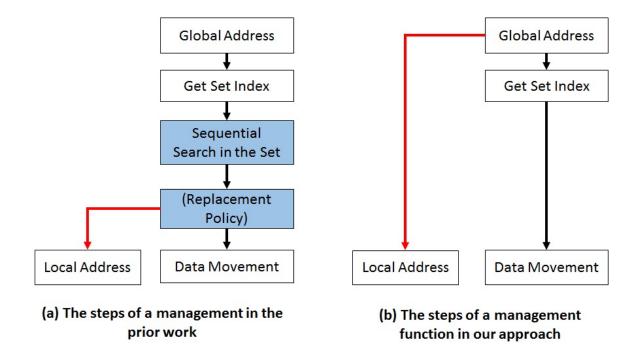

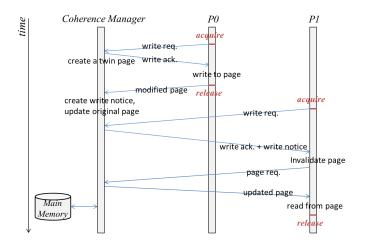

| 5.2  | The Way COMIC Works                                                   | 83 |

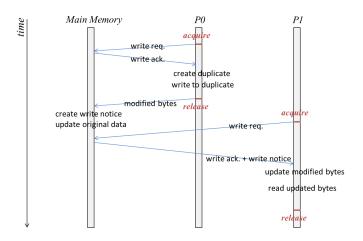

| 5.3  | The Way Our Approach Works                                            | 84 |

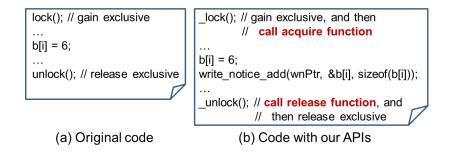

| 5.4  | Code Transformation With Our Management Functions                     | 85 |

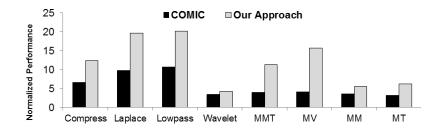

| 5.5  | Comparison Of The Performance Of Our Approach And COMIC               | 88 |

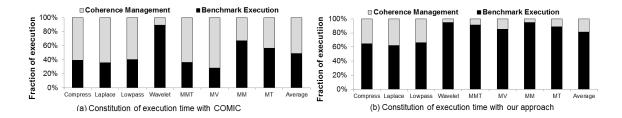

| 5.6  | The Comparison Of Runtime Overhead Of Our Approach And COMIC.         | 90 |

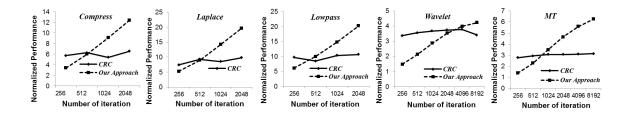

| 5.7  | Compute-intensity Is Varied By Changing The NumIters Parameter        | 91 |

#### Chapter 1

# INTRODUCTION

Multi/many-core processors have been widely used to improve processor performance, as gains from increasing operating frequency on uniprocessors gradually diminished. In a typical multi-/many-core processor, caches are used to store frequently accessed data to bridge the gap of processing speed and memory access latency. As a result, cache coherence is required to maintain coherence of shared data (which is cached in multiple cores), so that the semantics of applications running on the processors are not changed. Cache coherence largely improves programmability, as it hides the underlying details of the memory subsystem and creates an illusion of a single image of memory. However, it comes at a price—scaling cached-based architectures becomes increasingly difficult, as area and power overhead of implementing cache coherence increases rapidly as the number of cores grows Bournoutian and Orailoglu (2011); Choi et al. (2011); Garcia-Guirado et al. (2011); Xu et al. (2011). While designing scalable cache coherence mechanisms remains as an important research problem, many researchers pay attention to use more power-efficient fast memory instead of caches in processor designs. An noticeable example of such efforts is scratchpad memory (SPM).

# 1.1 Scratchpad Memory

An SPM is the local memory incorporated into a processor or System on Chip (SoC) architecture and controlled by software (the application itself, compiler, operating system, or a combination of them). SPMs can be found in many processors, such as in high performance computing Carter *et al.* (2013); REX Computing, Inc. (2014),

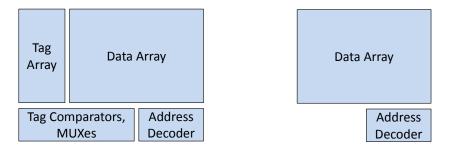

(a) Hardware Controlled Cache

Figure 1.1: Difference between cache and SPM—the hardware view: SPM is raw memory without the hardware mechanism to manage it (as is present in caches).

gaming and multimedia processing Gschwind *et al.* (2006b), and networking Olofsson (2016). SPM is attached to the processor in much the same way as an L1 cache. However, an SPM is a piece of raw memory, in the sense that it only contains decoding and column access logic, without the complex circuitry required to achieve hardware control of replacement policies, and managing coherence (tag directory, tag look-up circuitry, etc.). As Figure 1.1 shows, while a cache stores both the data and its address, an SPM only stores data, avoiding the extra lookup circuitry. As a result, SPMs use less area yet consuming significantly less power than caches (for the same data capacity) Banakar *et al.* (2002); Redd *et al.* (2014).

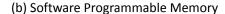

Functionally SPMs are similar to caches, in that they allow for fast access to frequently used data, but with lower power and latency. However, replacing caches with SPMs comes with its own set of challenges, as in Figure 1.2. Using caches is automatic; if desired data is not present in the cache, hardware mechanisms are built to bring the requested data into the cache, potentially preventing the necessity of a repeated operation if the data is reused. However, SPM contains no such hardware mechanism to automatically bring the data that is requested to the SPM. It must be brought in explicitly through memory transfer instructions that trigger DMA trans-

Figure 1.2: Difference between Cache and SPM—the software view: the data movement to and from the cache is performed automatically in hardware, in SPM-based systems, it must be present in the software in the form of data movement instructions.

fers. Furthermore, once data is brought in, it must be accessed using its new address in the SPM, and not the original address in the main memory.

While there are challenges in using SPMs instead of caches, the promise is the movement of application data (including code) on SPM is very flexible. Caches are a one-size-fits-all approach. They have one way of managing data, regardless of how the data is actually accessed. Whether some data is accessed randomly, or is accessed in a first-in-first-out manner, on a cache-based system, it will always be accessed in the manner implemented in hardware. On the other hand, users of SPMs can make use of application semantics and knowledge of data access patterns to create more efficient management of data, thereby enabling customization of data movement across the memory hierarchy. For example, stack data in SPMs can be managed on stack-frame level instead of cache blocks, as when a function call happens, it is likely that all the data within the stack frame will be needed during the execution of the function. By loading all the data in a stack frame at once, we can reduce the overhead for checking if the requested cache blocks during the execution of the function are already in the SPM. In addition, if we know multiple stack frames of function calls along some path in the call graph can be held in the SPM at the same time, we can bring all these stack frames from the main memory into the SPM at once, instead of fetching each of them separately. By doing so, we can further reduce number of memory transfers, and eliminate status checking of stack frames between these calls.

# 1.2 Software Managed Manycore and Its Management

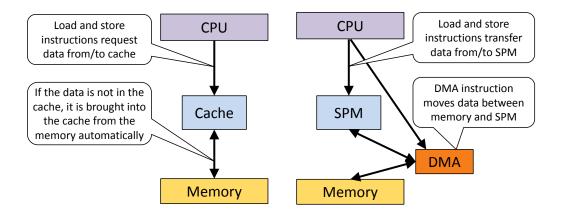

Figure 1.3: An example of SMM architectures.

Since code and data must be explicitly transferred by executing additional instructions to manage code and data between an SPM and main memory, SPM-based multi-/many-core architectures are called software managed manycore (SMM) architectures. Figure 1.3 shows an example of SMM architectures. In an SMM architecture, each core has a local SPM. A core can directly access the required code and data in slow main memory, or first load the code and data into its local SPM to improve performance. Code and data that are not immediately required can be evicted from SPM (to main memory).

To manage data on an SMM architectures, the space of an SPM is divided into different partitions, with one partition for code, stack, heap and global/static data correspondingly (each core runs one task at a time). Different management techniques are developed to manage each type of application data. The differences of management techniques are required due to the distinct characteristics of different types of data. For example, the addresses of stack variables in a stack frame is all based on the value of stack pointer, therefore we can easily change addresses of stack frames by simply changing the value of stack pointer. On the other hand, it is more difficult to change instruction addresses at runtime as doing so would affect PC(Program Counter)-relative memory accesses. Therefore, stack management techniques on SMM architectures can move stack frames to any available SPM or memory or memory locations at runtime, while code management techniques on SMM architectures typically uses the same address for different functions, and rely on a technique called overlaying to load only the required functions (thus evicting the functions currently occupying the same memory addresses) at runtime. Similarly, we can not simply apply the same techniques of stack or code management to manage heap data, as heap objects are generally scattered in memory. We need to develop different techniques for heap management, such as software caching.

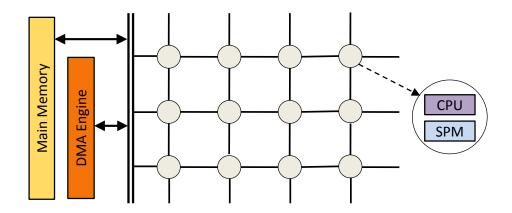

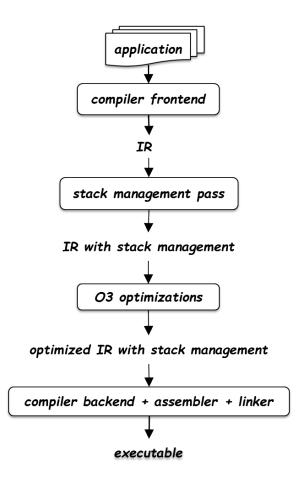

A big body of SPM management techniques for SMM architectures are compilerdirected, as inserting data movement operations by hand force programmers to trace flow of data, which can be error-prone. Early SPM management are mostly static approaches Panda *et al.* (1997); Sjödin and von Platen (2001); Avissar *et al.* (2001, 2002); Nguyen *et al.* (2005); Verma *et al.* (2003); Steinke *et al.* (2002b), which divides application data into SPM and memory. In other words, part of application data (typically most frequently accessed) goes to the fast SPM, while the rest is allocated and accessed in the slower main memory. Such techniques are limited as the size of application data grows, when most of the application data has to be directly accessed in main memory. Most recent works use dynamic techniques. Many dynamic techniques are driven by profiling Egger et al. (2008a, 2010); Ishitobi et al. (2010); Kandemir et al. (2001); Panda et al. (2000); Li et al. (2005a); Jia et al. (2015); Udayakumaran and Barua (2003); Dominguez et al. (2005); Udayakumaran and Barua (2006); Udayakumaran et al. (2006a); Dominguez et al. (2007); Verma and Marwedel (2006); Chakraborty and Panda (2012). Profilers are used to collect various information, such as loop bounds or outcomes of branches, provided representative program inputs are present. These information is then used to decide most frequently used data that can be stored in SPM, either statically or dynamically. Such approaches, while can be very efficient, cannot be applied when program behaviors change drastically when inputs vary, and are therefore lack of generality. To solve this problem, we present non-profiling-driven compiler-directed approaches to manage data movement between SPM and main memory, as in Figure 1.4. Such an approach takes as input a program, analyzes and inserts instructions for data transfers to the intermediate-representation (IR) of the program, and then generates the binary file for the SMM processors.

It is sometimes necessary to manage shared data in different cores, on top of the management of local data. This topic has been extensively studied in clusters. However, those approaches does not apply well to SMM architectures. In traditional clusters, inter-process communication is very expensive, while computation is relatively cheap thanks to powerful processors used in the clusters. Therefore, shared data management usually tries to minimize communication at the cost of introducing more computation. In SMM processors, however, inter-core communication becomes faster, while computation power of each core is weakened to save power. Instead, number of cores is increased to offset the lost of computation speed. Therefore, we developed a different approach that can significantly reduce computation overhead, even though it may increase data transfers among cores.

Figure 1.4: Our approach analyzes programs and inserts management instructions for efficient data movement between SPM and main memory.

## 1.3 Overview of This Thesis

This thesis develops efficient non-profiling-driven automatic compiler-directed data management techniques to manage different types of application data on SMM architectures. Chapter 2, 3, 4 and 5 explain the details and experimental results of the code, stack, heap and shared data management techniques developed in this thesis. Chapter ?? summarizes this thesis and introduces publications contribute to this thesis.

## 1.3.1 Efficient Code Management

One way to manage code on SMM architectures is to divide the space of each SPM into regions, and map the functions in a program into these regions. Each function is mapped to exact one region, and therefore multiple functions may be mapped to the same region, if there are more functions than regions, which is not uncommon as SPM space is typically limited, just like caches. Code management introduces overhead in the form of increased memory transfers and dynamic instructions. To reduce such overhead, we can either i) reduce memory transfers, or ii) reduce number of instructions executed. Existing code management techniques for SMM architectures focus on the first issue Lu *et al.* (2015a). In Chapter 2, we show the second issue is very important, introducing 22% extra instructions on typical embedded applications even when SPM size is larger than code size. Our technique reduces the instruction

overhead by 16% and execution time by 14% respectively, compared to managing code without solving the second issue. Our approach reduces execution time by 9% on average compared to caches, when only code management is considered, i.e. assume the accesses to the rest of application data always hits.

## 1.3.2 Efficient Stack Management

Stack management is also very important, as stack accesses account for around 64% of overall memory accesses Kannan *et al.* (2009) in Mibench Guthaus *et al.* (2001a), which consists of typical embedded applications. To ensure the functionality of applications, stack management techniques on SMM architectures have to i) copy stack frames between SPMs and main memories at right timing, and ii) solve the pointer corruption issue caused by changed addresses of stack variables. An existing work Lu *et al.* (2013) has solved the first problem efficiently. The solution to solve the second problem is however still relatively preliminary, focusing on correctness but not efficiency. In Chapter 3, we show an approach of efficient manage stack pointers that reduces execution time by 52% compared to the basic pointer management approach. Additional experiments show our approach reduces execution time by 12% on average compared to caches, when only stack data is considered, i.e. assume the accesses to the rest of application data always hits.

#### 1.3.3 Efficient Heap Management

Heap management on SMM architectures are mostly based on software caching, i.e. manage data movements between SPM and data in a way emulating how a cache works. Memory accesses are intercepted and replaced by management calls that transfers data between SPM and main memory when necessary. For example, one technique Bai and Shrivastava (2013) blindly intercepts all the memory accesses at runtime, and then filters non-heap accesses at run time. The management function treat an SPM as a 4-way set-associative cache and manages data accordingly. In Chapter 4, we develop a heap management that identifies heap objects and their alias at compile time, and eliminate most of runtime checking. Next, we reduce the instruction overhead of manage calls by emulating a direct-mapped cache, which does not require the sequential search of four entries in each set (assuming parallel search is not supported) and complex cache replacement policy. Furthermore, we inline the management calls and remove redundant steps. Finally, we show an optional optimization that relies on profiling. The experimental results show it reduces execution time of benchmarks by 80%. With the optional profile information, the reduction can be increased to 83%.

#### 1.3.4 Shared Data Management

Last but not least, we present a technique to manage shared data among different cores in SMM architectures. Traditional shared data management favors coarse-grain data movement, such as at page level, to reduce number of communication. Such coarse-grain data management typically ends up introducing more computation. For example, if multiple cores need to write to different locations of the same page, each core needs to create a local copy to work on, and finally compare it with the original page to apply the differences accordingly. This is necessary to avoid false sharing. However, the comparison of two pages is compute-intensive and is not efficient in SMM processors. We develop a technique that records the exact location and the size of each change, so that we can notify other cores about the exact changes to avoid transferring an entire page and comparing. While it may cause higher number of communication, the expensive page comparison is saved. The technique we developed achieved more than 2X speedup than the previous technique.

#### Chapter 2

# CODE MANAGEMENT ON SPM

#### 2.1 Introduction

The power and area overheads of cache coherence logic increase exponentially with the increasing number of cores, posing serious challenges in designing multicore architectures Bournoutian and Orailoglu (2011); Choi *et al.* (2011); Xu *et al.* (2011). Using scratchpad memories (SPMs), on the other hand, considerably simplifies the hardware by removing circuitry for tag comparison, replacement and coherence Banakar *et al.* (2002). The simplified hardware, however, shifts the work of memory management from hardware to software and requires executing additional management instructions in software. Multicore architectures based on SPMs are, therefore, called software-managed multicore (SMM) architectures. In an SMM architecture, each core has a local SPM. Instructions or data can be transferred into an SPM to reduce access latency, by direct memory access (DMA) operations.

One way to manage instructions on a local SPM is overlaying Levine (1999). Overlaying divides SPM space into different regions, with each function allocated to one of the region. Before every function call, additional code for calling the management function must be inserted. The management function checks the SPM state to see if the called function is loaded in the SPM and if not, performs a DMA operation. Similarly, the management function needs to be called again right before the called function returns back to the caller, because the caller function might have been evicted by the called function, in case they share the SPM space.

There are two sources of overhead in such code management. The long-latency

Figure 2.1: Code management increases instruction count by 22% on average even when the SPM is larger than the code size.

DMA operations are one source of overhead. The SPM allocation determines the sharing among functions, and a poor allocation scheme can increase the overhead of DMA operations by causing frequent reloading of functions. Another source of overhead comes with calling the management function at every call site. A management function call can cause a noticeable overhead even without any DMA operation, as it involves multiple table lookups for obtaining the information (allocated address, size, SPM state) of functions. If the required function is absent in SPM, the manage function will need to perform additional operations updating the SPM state after the loading operation.

Most previous code management efforts based on overlaying focus on the first overhead and try to find memory allocation schemes that avoid reloading functions frequently Pabalkar *et al.* (2008); c. Jung *et al.* (2010); Baker *et al.* (2010); Jang *et al.* (2012); Bai *et al.* (2013); Lu *et al.* (2015b). For example, allocating the caller and the called function in a loop to different memory addresses eliminates competition for SPM space between them, and thus is a desirable allocation scheme. These approaches, however, do not address the second overhead and blindly insert management function calls to every call site even though some of them may not be necessary. For instance, even if a function is loaded into its private space in the SPM, a management function has to be called every time the function is called, only to find out that the function is already loaded in the SPM. Figure 2.1 shows such overhead of executing code management instructions *in vain*. It shows that over a set of typical embedded programs Guthaus *et al.* (2001b), 18% of executed instructions on average are from management functions. Note that this is the *lower bounds* of the overhead when the SPM size is large enough to assign a private region to every function. For smaller SPM sizes, the number of loading operations will increase as the conflicts between functions increases, thus the overhead of executing management instructions, e.g. looking up function sizes and addresses for DMA operations, and updating the SPM state after DMA.

In this chapter, we present a compiler-based approach to reduce the overhead of management function calls. Given the allocation of functions to the SPM, our analysis statically determines whether a function can be safely assumed to be loaded before each call site. If a function is guaranteed to be already loaded at a call site, we label the call site as *always-hit* and do not insert a management function call. Similarly, a call site in a loop is labeled as *first-miss*, if the called function cannot be guaranteed to be always loaded but once loaded, is never evicted until the end of the loop. In this case, we place the management function call in the loop preheader to call the management function only once before entering the loop.

The static instruction cache analysis based on abstract interpretation Ferdinand and Wilhelm (1999); Cullmann (2013) also tries to identify always-hit and first-miss cache lines. However, within nested loops, their first-miss analysis Cullmann (2013) is only able to identify cache lines that are first-miss at the outermost loop. On the other hand, our first-miss analysis can identify any first-miss call site including those that are only first-miss within inner loops. In addition, our solution consists of two steps: i) static analysis for finding always-hits and first-misses; ii) inserting management function calls based on the analysis result. The cache analysis techniques only deal with the first part and cannot be directly used for reducing overhead of code management on SPM.

For evaluation, we use the state-of-the-art overlay-based function allocation technique Lu *et al.* (2015b), and various benchmarks from Mibench suite Guthaus *et al.* (2001b), with varying SPM sizes. The results show that our approach reduces the management overhead by 84%, and overall dynamic instruction counts by 16%. Consequently, execution time is reduced by 14% on average. In addition, our approach is able to reduce the execution time by 9% on average and up to 15% compared to hardware caching, even with conservative measurement.

# 2.2 Related Work

The early approaches on code management are based on static management Steinke et al. (2002b); Angiolini et al. (2004); Verma et al. (2004). In static management, a selected part of the code is loaded into the SPM only at loading time before the execution. These techniques can become inefficient for large programs when most of the code remains in the slow main memory.

Dynamic management techniques overcome this problem by loading instructions at run-time. A large body of these approaches Janapsatya *et al.* (2006); Verma and Marwedel (2006); Udayakumaran *et al.* (2006b); Steinke *et al.* (2002a); Egger *et al.* (2006, 2010), however, allocates only part of the code to the SPM, assuming that instructions can be directly fetched from the main memory as in ARM ARM (2004). These techniques first find a set of reloading points, and then determine the (frequently-used) code blocks to be loaded at each reloading point. Whenever the control reaches a reloading point, the corresponding loading operation is performed without checking the SPM state. Any instruction left in the main memory has to be fetched from the main memory. All these approaches are profiling-driven, and are not applicable if representative inputs of programs are not present.

Our analysis techniques directly target non-profiling-driven code management techniques Pabalkar *et al.* (2008); c. Jung *et al.* (2010); Baker *et al.* (2010); Jang *et al.* (2012); Bai *et al.* (2013); Lu *et al.* (2015b); Kim *et al.* (2014). All these approaches work at the granularity of function and conceptually perform as a direct-mapped cache where the entire code of a function is loaded into a cache line at once. Here, each cache line is called *region*, and management techniques find a *mapping* of functions to the regions with the goal of reducing the conflicts between functions. In this chapter, we apply our approach to the latest among these techniques Lu *et al.* (2015b) and compare the performance before and after using our approach for evaluation.

It is worth noting that the key idea of our approach is not limited to functionlevel code management approaches. Our analysis technique can be extended for any management techniques where code blocks are conditionally loaded after checking the SPM state.

Some approaches Francesco *et al.* (2004); Egger *et al.* (2008b) require hardware support such as MMUs, which may not be available in some processors Gschwind *et al.* (2006b); Texas Instrument (2014) and therefore are not considered in this chapter.

Previous code management techniques for SMMs solve the problem of "whereto-load" each function but not "when-to-load"; management functions are inserted blindly at every call site. Even with an ideal allocation where each function is assigned to a private region, management functions are executed before and after every function call, just finding out loading is unnecessary. On the other hand, the technique presented in this chapter focuses on reducing management instructions.

Figure 2.2: Our analysis avoids unnecessary management functions.

# 2.3 Motivating Example

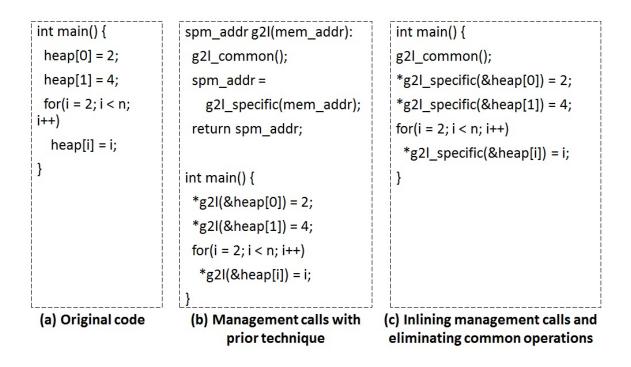

Figure 2.2 shows that current code management techniques may insert unnecessary management function calls, and how we can avoid them. The code management function, referred as  $\_get$  in the rest of our discussion, is inserted around each function call. The  $\_get$  function checks if the required function is currently in the region it is allocated to. If not, it loads the function into the SPM. The SPM space is divided into three regions  $r_0$ ,  $r_1$  and  $r_2$ . Functions are allocated to the regions respectively as follow:  $\{main\}$ ,  $\{F1,F3\}$ ,  $\{F0,F2\}$ . Previous code management approaches insert code management functions around each function call as in Figure 2.2(a). However, with proper analysis, we can remove some of code management function calls as

Figure 2.3: Overview of our approach.

Figure 2.2(b) shows. For example, throughout the execution, main will never be evicted since it is the only function mapped to  $r_0$ , so none of the calls of  $\_get(main)$ after each function call is necessary. Also, since we know F1 is the only function called within the loop in region  $r_1$ , it will not be evicted after it is loaded into the region for the first time. On the other hand, the  $\_get$  function called before each call to F0 and F2 in the loop are required, since the exact order of execution is not know at compile-time, so we have to conservatively assume either of them may be evicted in previous iterations from  $r_2$ .

## 2.4 Our Approach

Figure 2.3 shows the general flow of our approach. The compiler takes as input a program, and generates a control flow graph (CFG) for each function. All the CFGs, as well as the mapping between functions and regions, are then fed as input to our analyses. The output of our analyses are as follow: i) before each function call, whether the called function is always-hit/first-miss; ii) after the function call, whether the caller function is always-hit/first-miss. The result is then used to insert (necessary) code management functions accordingly.

#### 2.4.1 Notation

For ease of discussion, we define the following symbols. Let the set of regions the SPM space is divided into be  $R = \{r_1, ..., r_n\}$ , and the set of functions called in a program (including the main function) be  $F = \{f_1, ..., f_m\}$ . We define a SPM state as the function  $ss: R \to F$ . Given a region id  $r_x$ ,  $ss(r_x)$  returns the current function that owns this region. Each SPM state describes the memory state of the SPM at a certain moment in time—it specifies the current owner function in each region. In our analyses, we maintain an *in* and an *out* SPM state for each function, basic block, and call instruction, which record the current functions in the SPM before and after the function, basic block and call instruction, respectively. In particular, each call instruction maintains an extra *int* SPM state. It is used to record the state of the SPM right before the called function returns. The difference between *int* and *out* is as follow. Let  $F_x$  be the caller function of a call instruction, and  $r_x$  be the region  $F_x$  is mapped to. If the caller function is evicted during the execution of the called function, then  $int[r_x] \neq F_x$ . Right before the called function returns, the caller function must be brought to the SPM in order for the execution to continue. Therefore,  $out[r_x] \equiv F_x$ , while  $int[r_x]$  may not always be  $F_x$ . A helper function  $map: F \to R$  tells which region a function is mapped to.

Two SPM states can be joined via the following function:

$$\bigcup^{ah}(ss_1, ss_2) = \begin{cases} r_i \leftarrow ss_1(r_i) & \text{if } ss_1(r_i) = ss_2(r_i) \\ r_i \leftarrow null & \text{otherwise,} \end{cases}$$

and

$$\bigcup^{fm}(ss_1, ss_2) = \begin{cases} r_i \leftarrow ss_1(r_i) & \text{if } ss_1(r_i) = ss_2(r_i) \\ r_i \leftarrow ss_1(r_i) & \text{if } ss_2(r_i) = NULL \\ r_i \leftarrow ss_2(r_i) & \text{if } ss_1(r_i) = NULL \\ r_i \leftarrow null & \text{otherwise} \end{cases}$$

where  $r_i$  denotes the  $i_{th}$  region,  $1 \leq i \leq n$ . The  $\bigcup^{ah}$  operation keeps only a function when it appears in its mapped region on both SPM states. This is because for a function to be always-hit, it must has been loaded and not be evicted in all the possible paths leading to the program point. On the other hand,  $\bigcup^{fm}$  keeps a function when it is the only possible function in its mapped region of the two SPM states, since for a function to be first-miss, all we need is to ensure that it is impossible for the function to be evicted by other functions mapped to its region once it is loaded in a loop.

# 2.4.2 Always-hit Analysis

Algorithm 1 shows the procedure of always-hit analysis. simFunc serves as the entry point of the analysis. It repeatedly calls sim function to statically simulates the execution of *main* function and other functions called either directly or transitively by *main* and record changes of SPM states, until the output (*out*) SPM state of each call instruction does not change any more. Initially all the SPM states are empty.

Figure 2.4 shows an example of applying the analysis from Algorithm 1 to find always-hit functions. Initially only the *main* function is in the SPM. Every time a function is called, it becomes the current function of the region it is mapped to. We assume none of F0, F1 and F2 calls any functions, therefore, after they return, they are still current functions in corresponding regions. When a basic block has multiple

Figure 2.4: Always-hit program points in main function, given the overlaying (function-to-region mapping). The out SPM state of each basic block is shown at the edge leaving the basic block. f in the prefix denotes the output is for the first traversal, o denotes the output is for the other traversals, and f/o means the output are the same for both.

predecessors, all their output should be joined (line 10 to 14). Since Algorithm 1 ignores the output of the back edge of a loop (which are empty) when producing the input to the loop header during the first traversal (*skipBE* is set to *true* in line 2), the input to the loop header in the example is therefore the same as the output after the first call to F0. In the second traversal, the output of the back edge is used to join with the output of F0 before entering the loop (*skipBE* is set to *false* in line 4).

Figure 2.5: First-miss program points in loop L2 of main function.

The join operation however does not change the input, thus the other SPM states. Therefore, after the second traversal, the algorithm stops.

The identification of both always-hit and first-miss program points after the analysis stops is as follow: for each function call, if the called function is in the *in* state of a call instruction, then the program point before the function call is always-hit; if the caller function is in the *int* state, then the program point after the function call is always-hit. The program point before the call to F0 after the loop is categorized as always-hit, since F0 is in  $r_2$  within the *in* SPM state of the function call. Therefore, we do not need to insert  $\_get(F0)$  there. For the same reason, the management functions after every call that checks for *main* can be skipped.

#### 2.4.3 First-miss Analysis

First-miss analysis is performed following always-hit analysis Algorithm 2 explains the analysis. The entry point is at simLoop function, where each loop L of a program is singled out and passed to simL function, which statically simulates the execution of L and functions called transitively. The analysis is done on each loop individually and independent of other loops, so before the analysis for each loop starts, all the SPM states are reset as empty.

Figure 2.5 shows an example of applying Algorithm 2 to find first-miss program points in the outer loop L2. Again, we assume F0, F1 and F2 do not have any function calls. The output of the back edge of L2 (initially empty) is used as the input of its header, since we do not care about the SPM states before the loop (line 6). Since L2 must be executed within its parent function, main must have been brought into the SPM. Therefore, the in SPM state of the loop head becomes  $\{main\}, \{\}, \{\}\}$ . When entering loop L1, the output from its back edge is ignored when calculating the input to its loop header (line 10). This is because if any function is evicted in L1, it will not show up in *out* states of all the edges leaving L1. Disregarding the back edge therefore will not affect the correctness, since the eviction is already reflected in the forward edge(s). At the bottom of L1, SPM states of the two branches are joined by the  $\bigcup^{fm}$  operation. The output of loop L2 after the first iteration then becomes the input of its loop header when the second traversal starts. The same process is repeated, until all the output SPM states do not change.

The program point before the only call to F1 are first-miss in L2, since F1 is in  $r_1$ within the *in* SPM state of the call when the analysis for loop L2 stops. Notice that our first-miss analysis is done loop by loop, so while the program point before the call to F2 is not classified as first-miss in L2, it will be identified when the analysis runs on L1.

The first-miss analysis based on abstract interpretation Cullmann (2013) is done for all the loops at the same time. As a result, it is not able to identify program points before F2 in the above example to be first-miss in the inner loop L1, since the analysis finds out that F2 will be evicted in the outer loop L2 by F0. On the other hand, since our first analysis is done loop by loop, L2 is not considered during the analysis of loop L1. Therefore, it is able to identify F2 to be first-miss in the inner loop L1.

# 2.5 Evaluation

#### 2.5.1 Experimental setup

We run our always-hit and first-miss analysis on top of CMSM Lu *et al.* (2015b), the state-of-the-art function-level code management, and compare its performance with the original CMSM. We implement both approaches as transformation passes in LLVM compiler infrastructure Lattner and Adve (2004). We compile benchmarks from Mibench Guthaus *et al.* (2001b) with the passes enabled. Then, we run and collect performance statistics of generated binaries on gem5 CPU simulator Binkert *et al.* (2011b).

The CPU frequency is set to 3.2 GHz in gem5. We built an SPM along main memory, and implemented DMA operations. The cost of a DMA transfer consists of setup time and transfer time. The setup time is set to 91 nanoseconds (about 291 CPU cycles), and the data transfer is set to 0.075 nanoseconds per byte (0.24 CPU cycles) for each byte of data. These specs are borrowed to the well-known IBM Cell BE Processor Kistler *et al.* (2006).

Figure 2.6: Our approach reduces the management overhead by 84% and the overall execution time by 15% on average.

#### 2.5.2 Code Management Overhead Reduction

Figure 2.6 compares the dynamic instruction count before and after applying our techniques, both normalized to the dynamic instruction count of the original program without code management. The instruction counts for management functions calls are represented as red portions above 1, as overhead. The number of regions is set to the middle number between one and the number of functions of each benchmark. Such choice of the SPM size is for demonstration of the average-case performance between two extremes: i) the SPM space is so restrictive that all functions have to be mapped to one region, and ii) the SPM space is so large that each function can be placed in a separate region. Our approach reduces the number of instructions executed significantly, with the management instructions in most benchmarks almost eliminated, e.g. *basicmath*, *FFT* or *rijndael.enc*. Overall, as the rightmost columns show, the normalized dynamic instruction counts are decreased by 16% on average as a result of reducing 84% of the management overhead on average.

Benchmarks that receive insignificant overall performance improvement, such as *adpcm.dec* and *adpcm.enc*, have only a few function calls so the overhead of code management was already negligible before our approach. However, the management overhead is reduced over 99% in these benchmarks. For *stringsearch*, while it has many function calls, it has only three functions, with the *main* function calling the

Figure 2.7: Execution time is reduced by over 14% on average.

other two in a loop. Since there are only two regions (average of one and three), two of the three functions have to be mapped to one region, causing them to evict each other at every iteration. The management function calls are necessary and cannot be reduced.

Figure 2.7 shows the reduction in execution time after using our approach. On average, the execution time is reduced by more than 14%. The reduction in execution time is less than the reduction of dynamic instruct count. This is because management overhead includes both instructions and DMAs, and our approach only reduces management instructions.

#### 2.5.3 Comparison with Hardware Caching

We compare our approach with caching in a cache-based architecture. The cachebased system has a 2-way L1 instruction cache with 64-byte cache lines on gem5 simulator. The sizes of the SPM are the same as the experiments in section 2.5.2,

Figure 2.8: The execution times are normalized to those with hardware caching.

in which the number of regions is a half of the number of functions. Cache size for each benchmark is set to the smallest power of two that is no less than the SPM size. Cache miss latency is the same as the DMA setup time. This configuration is conservative since it leads to significantly larger cache sizes than SPM sizes in several benchmarks, *sha*, *IFFT*, *FFT*, *adpcm.dec* and *adpcm.enc*.

Figure 2.8 shows the normalized execution time of benchmarks with our approach compared to hardware caching. The overhead of code management in a cache-based architecture is measured as the number of cache misses times the cache miss penalty, while the overhead in the SMM architecture is measured as the sum of the time spent executing instructions of code management function calls and DMA cost.

In several benchmarks, using an SPM-based architecture with our approach can significantly reduce the execution time. However, caching is better in *adpcm.dec* and *adpcm.enc*, in which most of the execution time is spent on small loops that are small enough to fit in the instruction cache. However, even in these cases, the execution times are comparable, and the differences are not more than 6%.

## 2.6 Conclusion

In this chapter, we focus on management of code in SPM-based SMM architectures and present two analyses that find the locations where the outcomes of checking can be safely guaranteed and thus the management code can be removed or hoisted. With various benchmarks and various memory configurations, our experimental results show that our techniques can reduce the execution time by 14% on average. Using our approach on an SPM-based architecture, we observe that the execution times of benchmarks are significantly less or at least comparable to those on a cachebased architecture.

# Algorithm 1 Always-hit analysis

| 1:  | function SIMFUNC                                          |  |  |  |  |  |  |  |  |  |  |

|-----|-----------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| 2:  | sim(main,true)                                            |  |  |  |  |  |  |  |  |  |  |

| 3:  | while not converged do                                    |  |  |  |  |  |  |  |  |  |  |

| 4:  | sim(main, false)                                          |  |  |  |  |  |  |  |  |  |  |

| 5:  | 5: function $SIM(F, skipBE)$                              |  |  |  |  |  |  |  |  |  |  |

| 6:  | region = map(F)                                           |  |  |  |  |  |  |  |  |  |  |

| 7:  | F.in[region] = F                                          |  |  |  |  |  |  |  |  |  |  |

| 8:  | F.Entry.in = F.in                                         |  |  |  |  |  |  |  |  |  |  |

| 9:  | for each basic block $B$ in $F$ do                        |  |  |  |  |  |  |  |  |  |  |

| 10: | if $B$ is not $F.Entry$ then                              |  |  |  |  |  |  |  |  |  |  |

| 11: | if skipBE then                                            |  |  |  |  |  |  |  |  |  |  |

| 12: | $B.in = \bigcup_{Pa forward predecessor of B}^{ah} P.out$ |  |  |  |  |  |  |  |  |  |  |

| 13: | else                                                      |  |  |  |  |  |  |  |  |  |  |

| 14: | $B.in = \bigcup_{Pa \ predecessor \ of \ B}^{ah} P.out$   |  |  |  |  |  |  |  |  |  |  |

| 15: | for each call instruction $I$ in $B$ do                   |  |  |  |  |  |  |  |  |  |  |

| 16: | I.in = B.in or <i>out</i> of the previous call            |  |  |  |  |  |  |  |  |  |  |

| 17: | I.CalledFunction.in = I.in                                |  |  |  |  |  |  |  |  |  |  |

| 18: | sim(I.CalledFunction, skipBE)                             |  |  |  |  |  |  |  |  |  |  |

| 19: | I.int = I.CalledFunction.out                              |  |  |  |  |  |  |  |  |  |  |

| 20: | $I.out = I.int[region] \leftarrow F$                      |  |  |  |  |  |  |  |  |  |  |

| 21: | B.out = out of the last call                              |  |  |  |  |  |  |  |  |  |  |

| 22: | $F.out = \bigcup_{R  a  return  instruction}^{ah} R.out$  |  |  |  |  |  |  |  |  |  |  |

| Algorithm 2 First-miss analysis                                                     |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1: function SIMLOOP                                                                 |  |  |  |  |  |  |  |  |

| <b>for</b> each loop $L$ in the program <b>do</b>                                   |  |  |  |  |  |  |  |  |

| while not converged do                                                              |  |  |  |  |  |  |  |  |

| 4: $\operatorname{simL}(L)$                                                         |  |  |  |  |  |  |  |  |

| 5: function $SIML(L)$                                                               |  |  |  |  |  |  |  |  |

| : $L.Header.in = L.BackEdge.output$                                                 |  |  |  |  |  |  |  |  |

| 7: $L.Header.in[region] = F, the parent function of L$                              |  |  |  |  |  |  |  |  |

| 8: <b>for</b> each basic block $B \in L$ <b>do</b>                                  |  |  |  |  |  |  |  |  |

| 9: <b>if</b> $B$ is not $L$ . Header <b>then</b>                                    |  |  |  |  |  |  |  |  |

| 10: $B.in = \bigcup_{P \ a \ forward \ predecessor \ of \ B, \ P \in L}^{fm} P.out$ |  |  |  |  |  |  |  |  |

| 11: <b>for</b> each call instruction $I$ in $B$ <b>do</b>                           |  |  |  |  |  |  |  |  |

| 12: $I.in = B.in \text{ or } out \text{ of the previous call}$                      |  |  |  |  |  |  |  |  |

| 13: $I.CalledFunction.in = I.in$                                                    |  |  |  |  |  |  |  |  |

| 14: $sim(I.CalledFunction, true)$                                                   |  |  |  |  |  |  |  |  |

| 15: $I.int = I.CalledFunction.out$                                                  |  |  |  |  |  |  |  |  |

| 16: $I.out = I.int[region] \leftarrow F$                                            |  |  |  |  |  |  |  |  |

| 17: $B.out = out \text{ of the last call}$                                          |  |  |  |  |  |  |  |  |

## Chapter 3

## STACK MANAGEMENT ON SPM

## 3.1 Introduction

Low-power, yet high core-count embedded processors cannot afford the overhead of coherent caches Bournoutian and Orailoglu (2011); Choi *et al.* (2011); Garcia-Guirado *et al.* (2011); Xu *et al.* (2011). The scratchpad memory (SPM) based system is a promising alternative, as it provides a fast, low-power, and scalable memory hierarchy—the SPM has 34% less area and consumes 40% less power than a cache of the same capacity Banakar *et al.* (2002). Using SPMs instead of caches not only improves power, but also greatly simplifies the hardware design (and verification). SPMs shift the task of data management from hardware to the software, and therefore, multicore architectures with SPM-based memory hierarchy are termed Software Managed Multicore (SMM) architectures.

In SMM architectures, a core has to fetch data it needs to its local SPM before accessing it. Therefore we need techniques to manage data transfers between the SPM and the main memory. Among all the different types of data (heap, stack or global) to manage, optimized data management for stack data is especially important for performance. Kannan *et al.* (2009) shows (via profiling) that stack accesses account for around 64% of overall data accesses in Mibench, a benchmark suite of typical embedded applications Guthaus *et al.* (2001c).

State-of-the-art techniques to manage stack data on SMM architectures move stack data between SPM and main memory at the function call level. Therefore, these techniques need to solve two inter-related problemsBai *et al.* (2011). **i)** Stack

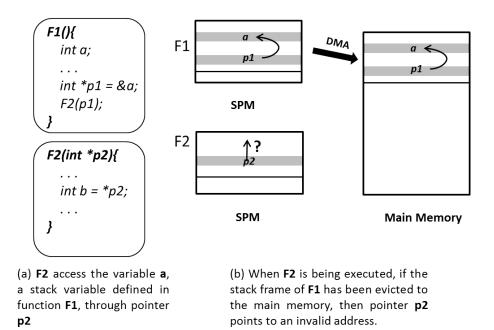

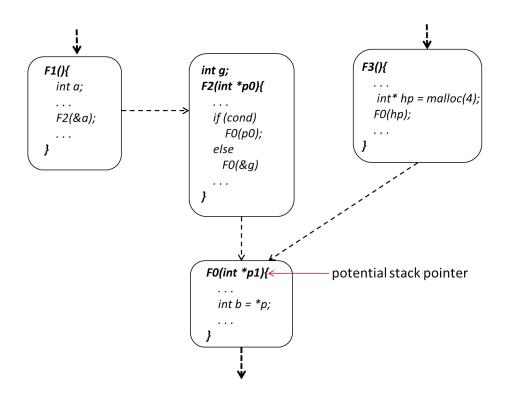

Figure 3.1: Pointer management problem.

frame management: stack frame of the function that is going to be executed must be brought into the SPM before it executes, and the stack frames of the functions that are not immediately needed may be evicted to the main memory. **ii) Pointer management:** if a stack frame of a function was evicted to the main memory, and the currently executing function accesses a local variable of the evicted stack frame (typically through a pointer), then the access is invalid, as shown in figure 3.1. This is because the pointer still contains the address of the local variable in the SPM before it is evicted. It is therefore vital to correct the address of the pointer, as otherwise the result of the execution will be incorrect.

A previous work, Bai *et al.* (2011) solves the problem of pointer management, by instrumenting the code to translate the pointer address at each definition and use—A definition refers to the write of a new value to the pointer, while a use refers to the read of the value defined by the reaching definition or the last write. While this enables correct execution, it incurs high performance penalty. In this chapter, we present an efficient compiler technique for managing pointers to stack data on SMM architectures. The two key ideas of our approach are: i) instead of translating the pointer address at each use of the pointer inside a function, we translate it only once when it is passed as the argument of the function. As a result, our technique is able to remove a significant portion of the overall translations. ii) if the stack frame of the function whose local variables are being accessed through pointers is guaranteed to be present in the SPM, then when any of the pointers is accessed, no translation is needed.

Experiments on benchmarks from the MiBench suite Guthaus *et al.* (2001c) show that our approach almost completely eliminates the pointer management overhead, and results in 52% reduction of the average execution time, as compared to the stateof-the-art pointer management technique Bai *et al.* (2011) on top of the state-of-theart stack frame management technique Lu *et al.* (2013) on SMM architectures. We also compare the performance of our stack pointer management on SPM with that on a cache-based architecture. Even with conservative estimates, stack data management on SPM outperforms stack data management on a cache-based architecture by 12% on average.

#### 3.2 Related Work

Stack management techniques in general can be divided into static approaches and dynamic approaches. Static approaches Avissar *et al.* (2002); Verma *et al.* (2003); Nguyen *et al.* (2005) map the most frequently used data to SPM and keep the allocation fixed throughout execution, while dynamic approaches allow the changes to the locations of stack data at run-time. Static approaches do not perform well since they do not take dynamic program behaviors into consideration. As a result, most recent works focus on dynamic SPM management techniques.

Many dynamic techniques Mamidipaka and Dutt (2003); Poletti et al. (2004); Park et al. (2007); Cho et al. (2007); Dominguez et al. (2007); Kandemir et al. (2001); Li et al. (2005b); Udayakumaran et al. (2006c); Gauthier and Ishihara (2011); Kannan et al. (2009); Bai et al. (2011); Lu et al. (2013) have been developed to manage stack data on SPM. Mamidipaka and Dutt (2003); Poletti et al. (2004); Park et al. (2007); Cho et al. (2007) introduce new hardware functionality to manage the SPM, while the interest of this chapter lies in providing software solution to simplified hardware. Among software solutions, Kandemir et al. (2001) and Li et al. (2005b) target on arrays specifically, Dominguez et al. (2007) mainly focuses on managing stack data for recursive functions on SPM, while we manage all the data in stack. Udayakumaran et al. (2006c) and Gauthier and Ishihara (2011) both rely on profile information, therefore the input has to be representative for either of them to deliver high-quality output, which is generally difficult. In addition, both approaches have limited support for pointer management. Udayakumaran et al. (2006c) relies on pointer analysis to identify and translate the address for any pointer that refers to the variable that is moved from the main memory to the SPM. If the point analysis fails to identify any such accesses through pointers and thus the requested memory addresses are not translated, the execution may fail, since these accesses end up accessing incorrect locations. Gauthier and Ishihara (2011) simply does not support using stack pointers as call arguments. In this chapter we are interested in generic approaches of stack management that do not rely on profiling or pointer analysis, and are able to manage pointers correctly. To our best knowledge, only the Circular Stack Management (CSM) Kannan et al. (2009); Bai et al. (2011); Lu et al. (2013) approaches provide such solution. In this chapter we will compare our work with Lu et al. (2013), which is the latest CSM work with the best performance.

(b) Illustration of pointer management functions.

Figure 3.2: The way pointer management functions work.

#### 3.3 Background

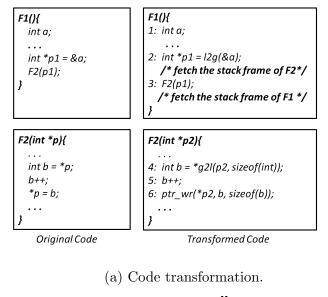

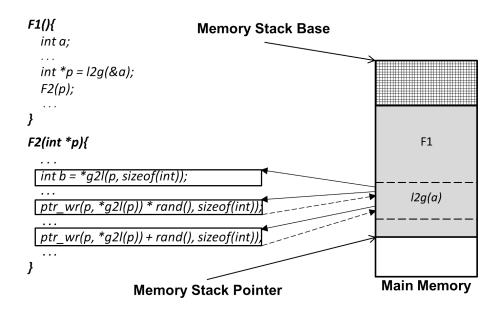

All the CSM techniques use the pointer management presented in Bai *et al.* (2011). The pointer management maintains two stack pointers: one in SPM and one in main memory ( assume the stack grows from the higher address (stack base) to the lower address (stack top)). It uses three pointer management functions: *l2g, g2l*, and *ptr\_wr*.

Figure 3.2 explains the functionality of these pointer management functions. Figure 3.2a shows the original code and the transformed code with pointer management. Figure 3.2b illustrates  $l_{2q}$  and  $q_{2l}$  calls at line 2 and line 4 in the transformed code respectively, assuming the SPM is not large enough to hold both the stack frames of function F1 and F2. When F1 calls F2, the stack frame of F1 must be evicted from SPM to the main memory to make space. The SPM address of stack variable a defined in F1 which is passed to F2 will become an invalid reference by the time it is accessed, since the entire frame of F1 (thus the the stack variable a) will have been moved to the main memory. In this case, l2g function should be called on a in F1 to calculate the address of the actual location of a in the main memory (line 2 in the transformed code in Figure 3.2a). Notice when  $l^2q(a)$  is called, the stack frame of F1 has not been evicted to the main memory yet. Therefore, the value of  $l^{2}g(a)$  indicates the memory location a will be moved to. At that time,  $l^{2}g(a)$  is smaller than the value of the memory stack pointer, and their distance is the same as the difference between the value of the SPM stack base and the SPM address of a, as offset in Figure 3.2b indicates (the upper figure of Figure 3.2b). After F1 is evicted to the main memory, the value of memory stack pointer is decreased by the size of the stack frame of F1. Consequently,  $l^2g(a)$  refers to the actual location of a, which becomes larger than the value of memory stack pointer (the lower figure of Figure 3.2b).

The result of l2g(a) is passed as an argument to F2 as its parameter p. F2 then calls g2l function before dereferencing it (line 4 in the transformed code). Since cores cannot access main memory directly, g2l(p) allocates a local buffer in SPM, followed by a DMA instruction to read the value from the main memory location specified by p-or equally l2g(&a)—and then return the address of the local buffer. The correct value can then be read from the local buffer. Finally, F2 modifies the value pointed by p, and calls  $ptr_wr$  to write back the modification from SPM to main memory (line 6 in the transformed code).

Pointer management functions will not alter program semantics. Consider the example in Figure 3.2 again, but this time we assume that the SPM is large enough to hold the stack frames of both F1 and F2. Therefore, when F2 is called, the stack frame of F1 is still in the SPM, and we can safely remove the stack frame management around line 3 at the transformed code in Figure 3.2a. In such a case, the call to g2lin F2 (line 4) will do nothing but reverting the address translation done by the  $l_{2q}$ function in F1 (line 2), and reading from the SPM address of a, which is the input to the  $l_{2g}$  function. Similarly,  $ptr_wr$  will revert the translation and write to the SPM address of a directly. Whether a stack variable has been evicted from the SPM to the main memory can be told as below. If an address that is passed to g2l or  $ptr_wr$ is smaller than or equal to the value of memory stack pointer, then the stack variable the address refers (thus the enclosing stack frame) is still in the SPM. In this case, g2l or  $ptr_wr$  just need to revert the address translation done by l2g and read from or write to the SPM address. Otherwise, if the address is greater than the value of the memory stack pointer, then the stack variable has been evicted, and q2l and  $ptr_wr$ will go ahead and perform required DMA operations. Therefore, even though pointer management from Bai et al. (2011) unnecessarily inserts extra pointer management functions, it can still ensure the correctness of the execution of programs.

Figure 3.3: The key ideas of our approach.

Pointer management from Bai *et al.* (2011) solves the problem for correctness, but not for performance. On the other hand, our approach removes unnecessary calls to pointer management functions and improves performance of applications noticeably.

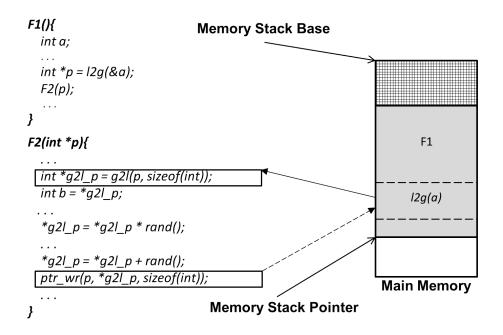

## 3.4 Key Ideas of Our Approach

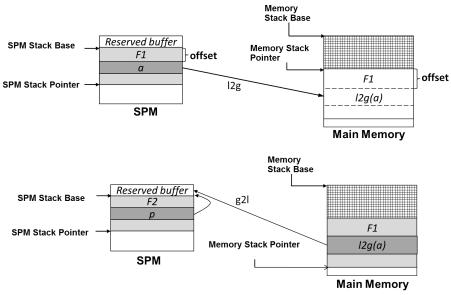

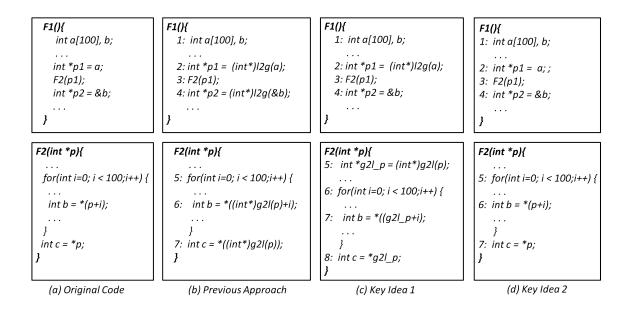

While the state-of-the-art pointer management from Bai *et al.* (2011) solves the pointer corruption issue correctly, it calls the l2g function at every definition of stack data pointers, and the g2l function on every use of the pointers, and results in unnecessary calls to pointer management functions, which eventually slows down the execution of programs.

Figure 3.3a and 3.3b show the original code and the code with the pointer management from Bai *et al.* (2011). The calls to l2g in line 4 in Figure 3.3b is not necessary, since the pointer p2 is only used in the same function the variable *b* is defined. Meanwhile, although the calls to g2l in line 6 is necessary, it can be promoted to be outside of the loop to avoid repeated computations. Notice the calls to g2l in line 6 can not be eliminated or reduced by standard compiler optimizations such as common subexpression elimination or loop invariant code motion. This is because g2lfunction needs to access some global states (implemented as global/static variables), such as the current values of the stack pointers, which could be changed by function calls and stack frame management between any two consecutive g2l calls. These interactions with global states prevent standard compiler optimizations from removing or relocating g2l calls, since the compiler cannot guarantee the changes will not cause any unexpected side effect to the semantic of programs.

This work aims to reduce these overheads based on two key ideas: i) we only manage pointers when they are used as call arguments instead of each of the uses, so that we only need to translate once at the caller and the called function respectively. ii) if the stack frame of a function is definitely in the SPM, then any accesses via pointers to the local variables in the stack frame do not need management. Figure 3.3c demonstrates the first idea. Instead of calling  $l_{2q}$  on every definition of pointers (line 2 and 4 in Figure 3.3b), we only call  $l_{2q}$  once in F1 when it calls F2 and passes a pointer-type argument (line 2 in Figure 3.3c). Also, we only call g2l function once at the beginning of F2 and reuse the result (line 5, 7 and 8 in Figure 3.3c), instead of calling it for every use (line 6 and 7 in Figure 3.3b). The q2l function is called outside the for loop to reduce overhead. Figure 3.3d shows the further optimized code with the second idea. If we know for sure the stack frames of F1 is in the SPM when F2 is called, then no stack frame management is needed, neither the pointer management—the references to the array a of F1 through pointer p in F2 will be guaranteed to access the correct locations, as the stack frame of F1 is not moved. The code in Figure 3.3d becomes exactly the same as the original code. In other words, it eliminates the overhead of stack management—both stack frame management and pointer management.

Figure 3.4: Identification of the potential pointer to stack.

- 3.5 Details of Our Approach

- 3.5.1 Steps of Our Approach

To achieve the efficient pointer management, our approach takes three steps. First, we need to decide if any pointer-type arguments of a function can be potential references to stack variables. Second, we will run the analysis to divide function calls in the call graph into groups, so that all the stack frames of each group can fit into the SPM at once. In the last step, we insert pointer management functions properly based on the previous analyses.

#### Identifying Stack Data Pointers at Function Calls

First of all, we perform an inter-procedural analysis to find out if any pointer-type arguments at function calls are potentially referring to stack variables. A function may be called at multiple locations during the execution of a program, therefore the same parameter may refer to multiple arguments that can be stack, heap or global variables, depending on the control flow at run-time. Consider the call graph in Figure 3.4. When F0 is called, the type of the argument that is referred by the parameter p1 may have three different types. If the control flow comes from F2, and cond is evaluated to be true in F2, then the argument passed to F0 is a pointer to stack variable a, which is defined in F1 and passed to F2 when it is called; Otherwise, if the control flow comes from F3 to F0, then p1 in F0 refers to the heap data referred by hp in F3. Since the actual control flow is not known at compile-time, we have to conservatively assume p1 refers to a stack variable.

To accomplish such analysis, we first go though all the functions and identify all the pointer-type formal parameters. Once we find such a parameter, we check all the call sites of the function, and find out all the possible arguments. Any of these arguments that refers to stack data needs to be managed.

Several cases pose challenges for this analysis. When a pointer to stack data is passed as an argument to a recursive function, then we need to call l2g on the pointer, and call g2l on the result of l2g function that is passed to the called function in the called function. This is because we do not know how many times the recursion will happen at compile time, so we need to conservatively assume the stack frame of the caller is evicted when the called function is executed. When the type of the variable a pointer refers to cannot be identified, we conservatively assume it is a stack pointer

Figure 3.5: The analysis to find out at which stack frames will exist in SPM at the same time.

and manage it.

# **Identifying Coexistent Stack Frames**

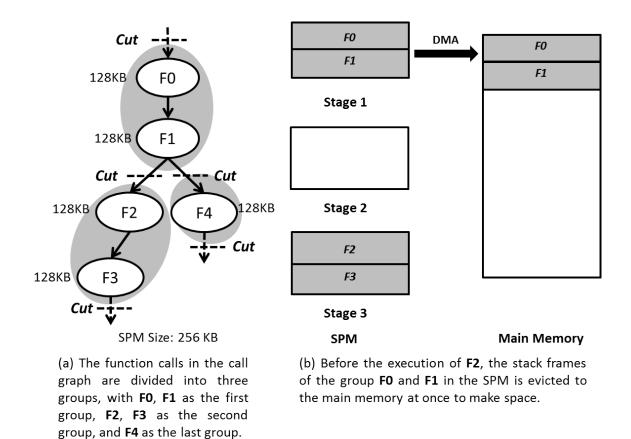

This step decides which stack frames can exist in SPM at the same time. We use the same analysis from Smart Stack Data Management heuristic (SSDM)Lu *et al.* (2013). Here we just explain the high-level idea. Details of the algorithm can be found in Lu *et al.* (2013).

The general idea of SSDM is that instead of managing stack frames one at a time at every function call, we can manage multiple stack frames of consecutive function calls along any path of a call graph at the same time. Instead of evicting the stack frame of the caller function from the SPM to main memory to make space for the called function whenever a function call happens, we can keep allocating SPM space for stack frames of function calls, and perform the stack frame management all at once only when there is not enough SPM space.